RL78/F13, F14 CHAPTER 19 DTC

R01UH0368EJ0210 Rev.2.10 1442

Dec 10, 2015

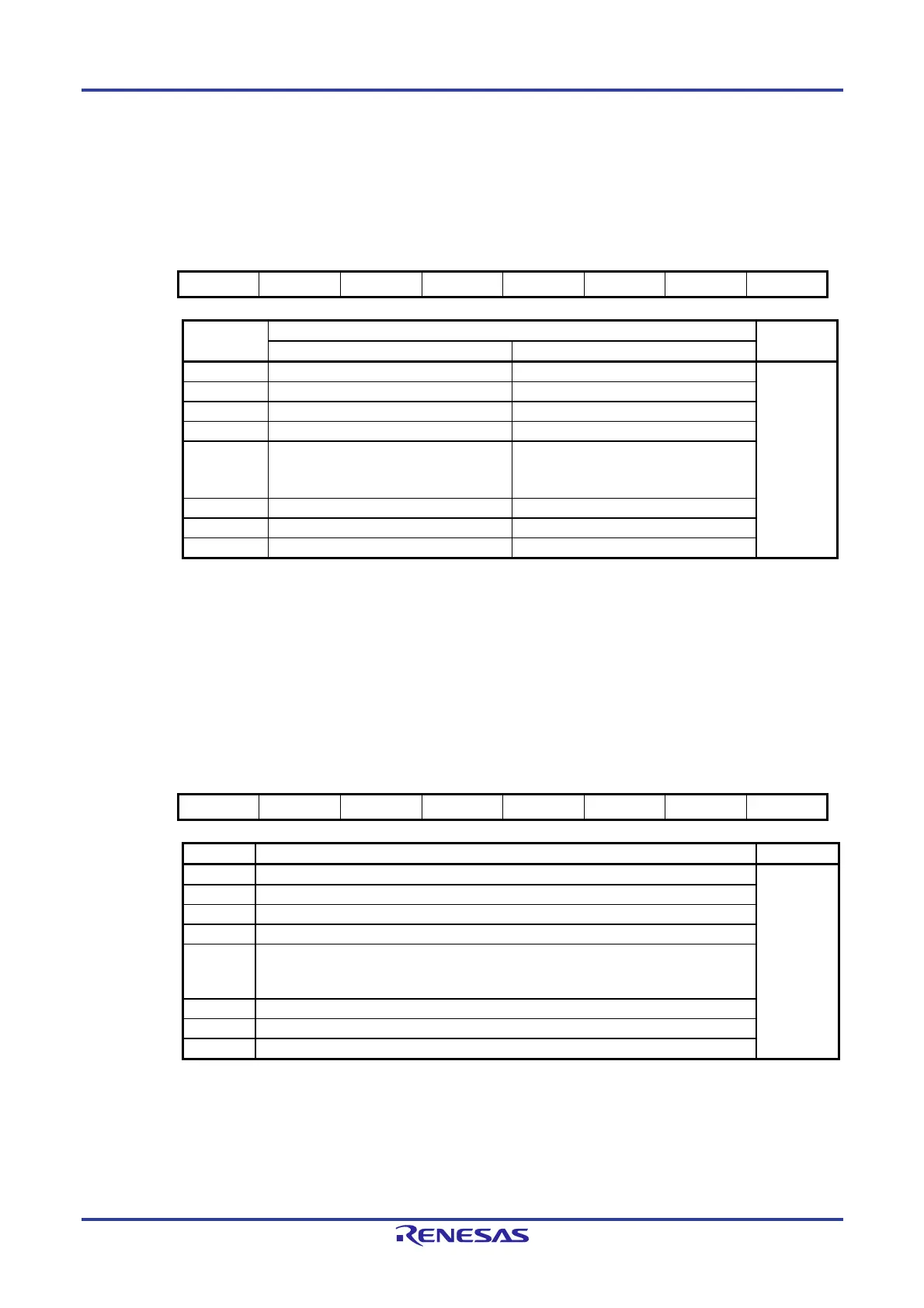

19.2.8 DTC Block Size Register j (DTBLSj) (j = 0 to 23)

This register is used to set the block size of the data to be transferred by one activation.

Figure 19-8. Format of DTC Block Size Register j (DTBLSj)

Address: Refer to 19.2.2 DTC Control Data Allocation. After reset: Undefined

Symbol 7 6 5 4 3 2 1 0

DTBLSj DTBLSj7 DTBLSj6 DTBLSj5 DTBLSj4 DTBLSj3 DTBLSj2 DTBLSj1 DTBLSj0

DTBLSj Transfer Block Size R/W

8-Bit Transfer 16-Bit Transfer

00H 256 bytes 512 bytes R/W

01H 1 byte 2 bytes

02H 2 bytes 4 bytes

03H 3 bytes 6 bytes

·

·

·

·

·

·

·

·

·

FDH 253 bytes 506 bytes

FEH 254 bytes 508 bytes

FFH 255 bytes 510 bytes

Caution Do not access the DTBLSj register using a DTC transfer.

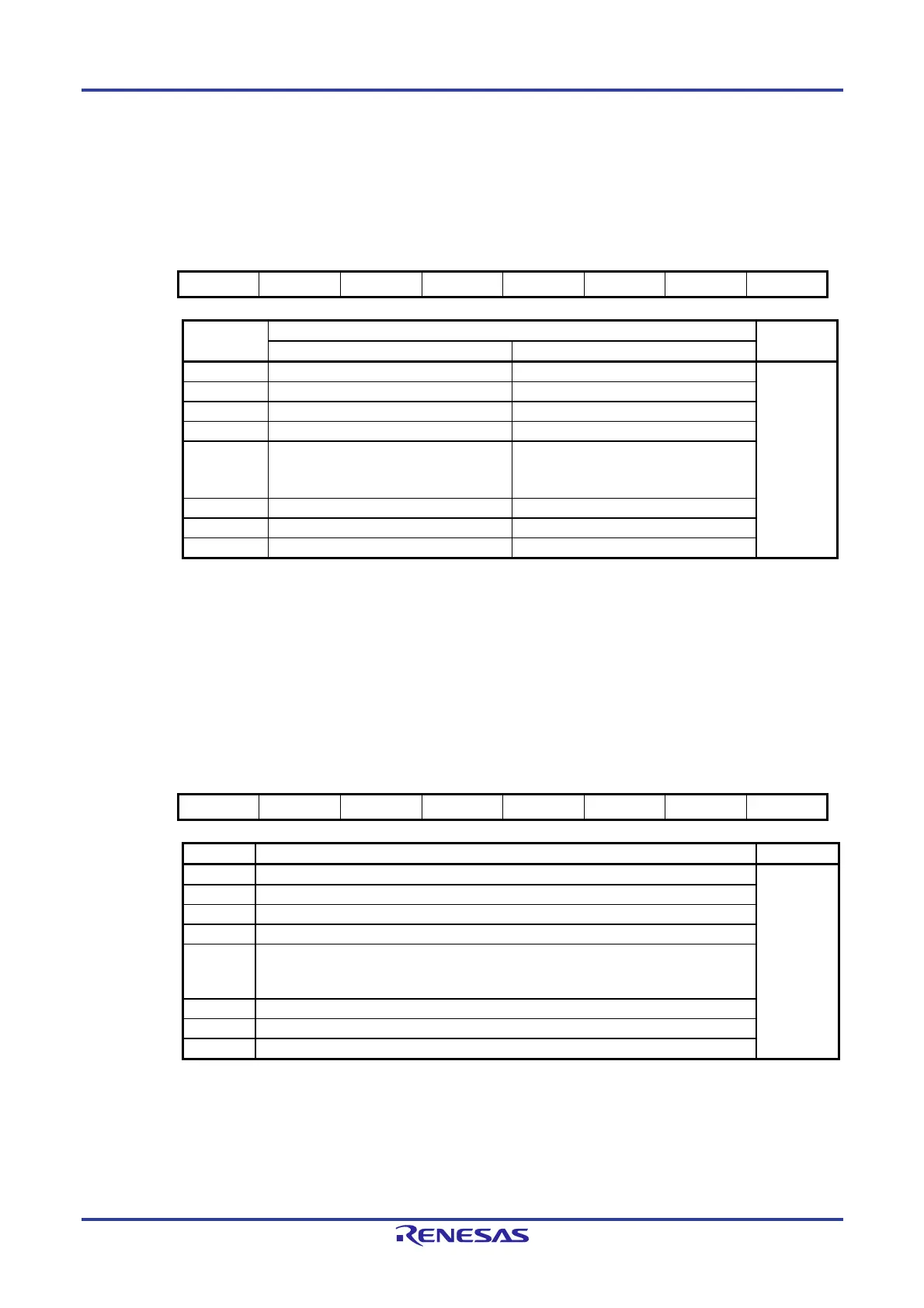

19.2.9 DTC Transfer Count Register j (DTCCTj) (j = 0 to 23)

This register is used to set the number of DTC data transfers. The value is decremented by 1 each time DTC transfer is

activated once.

Figure 19-9. Format of DTC Transfer Count Register j (DTCCTj)

Address: Refer to 19.2.2 DTC Control Data Allocation. After reset: Undefined

Symbol 7 6 5 4 3 2 1 0

DTCCTj DTCCTj7 DTCCTj6 DTCCTj5 DTCCTj4 DTCCTj3 DTCCTj2 DTCCTj1 DTCCTj0

DTCCTj Number of Transfers R/W

00H 256 times R/W

01H Once

02H 2 times

03H 3 times

·

·

·

·

·

·

FDH 253 times

FEH 254 times

FFH 255 times

Caution Do not access the DTCCTj register using a DTC transfer.

Loading...

Loading...