RL78/F13, F14 CHAPTER 21 INTERRUPT FUNCTIONS

R01UH0368EJ0210 Rev.2.10 1502

Dec 10, 2015

21.3.6 Interrupt mask register (INTMSK)

The interrupt mask register in the interrupt control circuit is used to mask interrupt requests corresponding to an INTPn

interrupt that is to be used as an event signal for the ELC or a source for DTC activation.

Set this register when the INTP4 to INTP6 signals are used not as interrupt sources for the interrupt control circuit but as

only ELC event signals or DTC activation sources.

This register can be set by an 8-bit memory manipulation instruction

Reset signal generation sets this register to FFH.

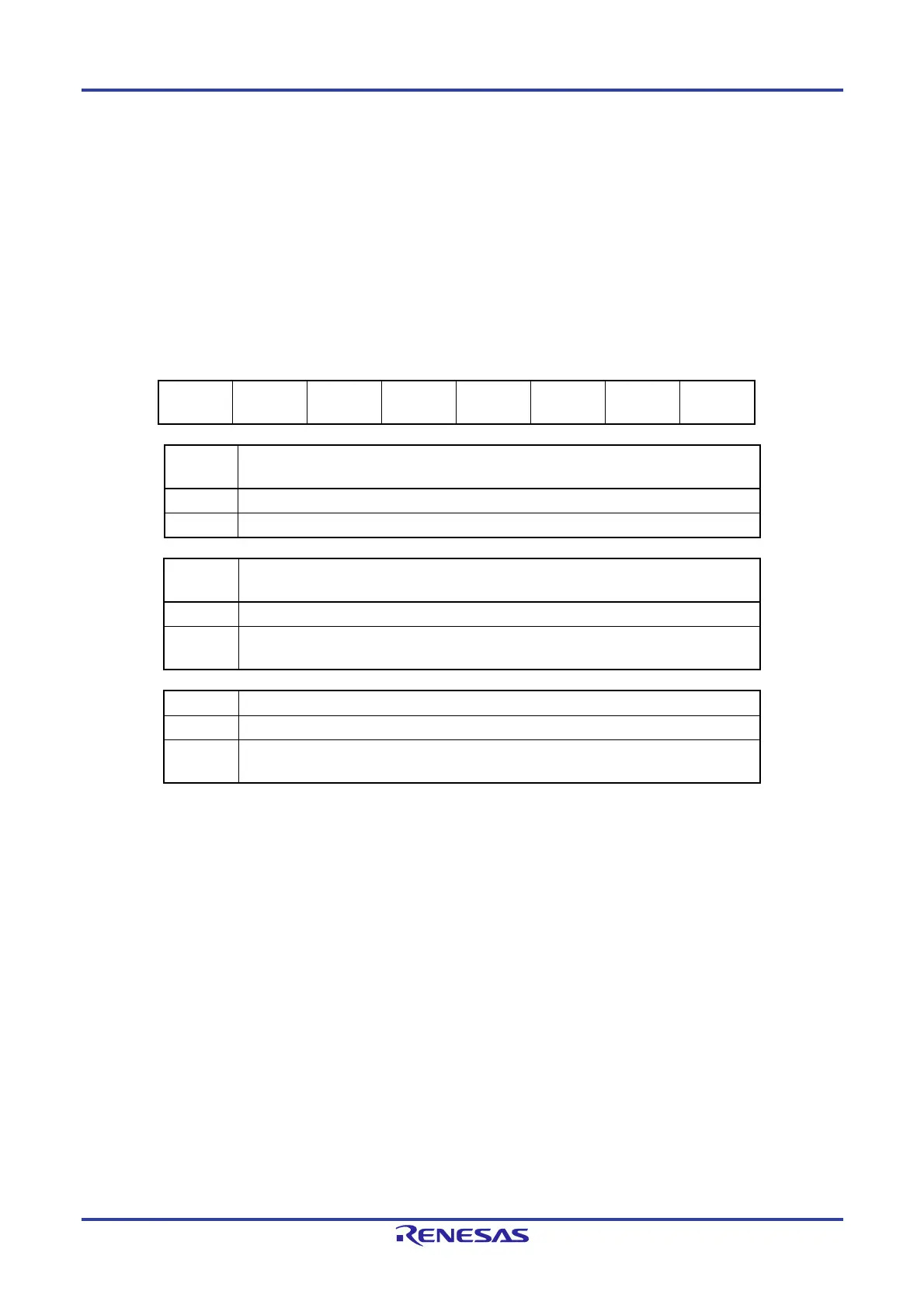

Figure 21-8. Format of Interrupt Mask Register (INTMSK)

Address: F007CH After reset: FFH R/W

Symbol 7 6 5 4 3 2 1 0

INTMSK 1 1 1 1 1

INTMSK2

Notes 1, 2

INTMSK1

Note 1

INTMSK0

INTMSK2

Notes 1, 2

Setting masking for INTP6 interrupt source to the interrupt control circuit

0 Requests to the interrupt control circuit and DTC are enabled.

1 Requests to the interrupt control circuit are disabled, and requests to DTC are enabled.

INTMSK1

Note 1

Setting masking for INTP5 interrupt source to the interrupt control circuit

Note 3

0 Requests to the interrupt control circuit, ELC, and DTC are enabled.

1

Requests to the interrupt control circuit are disabled, and requests to ELC and DTC are

enabled.

INTMSK0 Setting masking for INTP4 interrupt source to the interrupt control circuit

Note 3

0 Requests to the interrupt control circuit, ELC, and DTC are enabled.

1

Requests to the interrupt control circuit are disabled, and requests to ELC and DTC are

enabled.

Notes 1. Not provided in the 20-pin products.

2. Not provided in the products with 30 or 32 pins.

3. If an INTPn interrupt is generated, the bit m in the interrupt source determination flag register 0

(INTFLG0) is set regardless of the setting of the bit in the interrupt mask register.

n: INTP interrupt number (n = 4, 5), m: Bit number (m = 0,1)

Loading...

Loading...