RL78/F13, F14 CHAPTER 15 SERIAL ARRAY UNIT

R01UH0368EJ0210 Rev.2.10 812

Dec 10, 2015

15.3.6 Serial flag clear trigger register mn (SIRmn)

The SIRmn register is a trigger register that is used to clear each error flag of channel n.

When each bit (FECTmn, PECTmn, OVCTmn) of this register is set to 1, the corresponding bit (FEFmn, PEFmn,

OVFmn) of the serial status register mn is cleared to 0. Because the SIRmn register is a trigger register, it is cleared

immediately when the corresponding bit of the SSRmn register is cleared.

Set the SIRmn register by a 16-bit memory manipulation instruction.

Set the lower 8 bits of the SIRmn register with an 8-bit memory manipulation instruction with SIRmnL.

Reset signal generation clears the SIRmn register to 0000H.

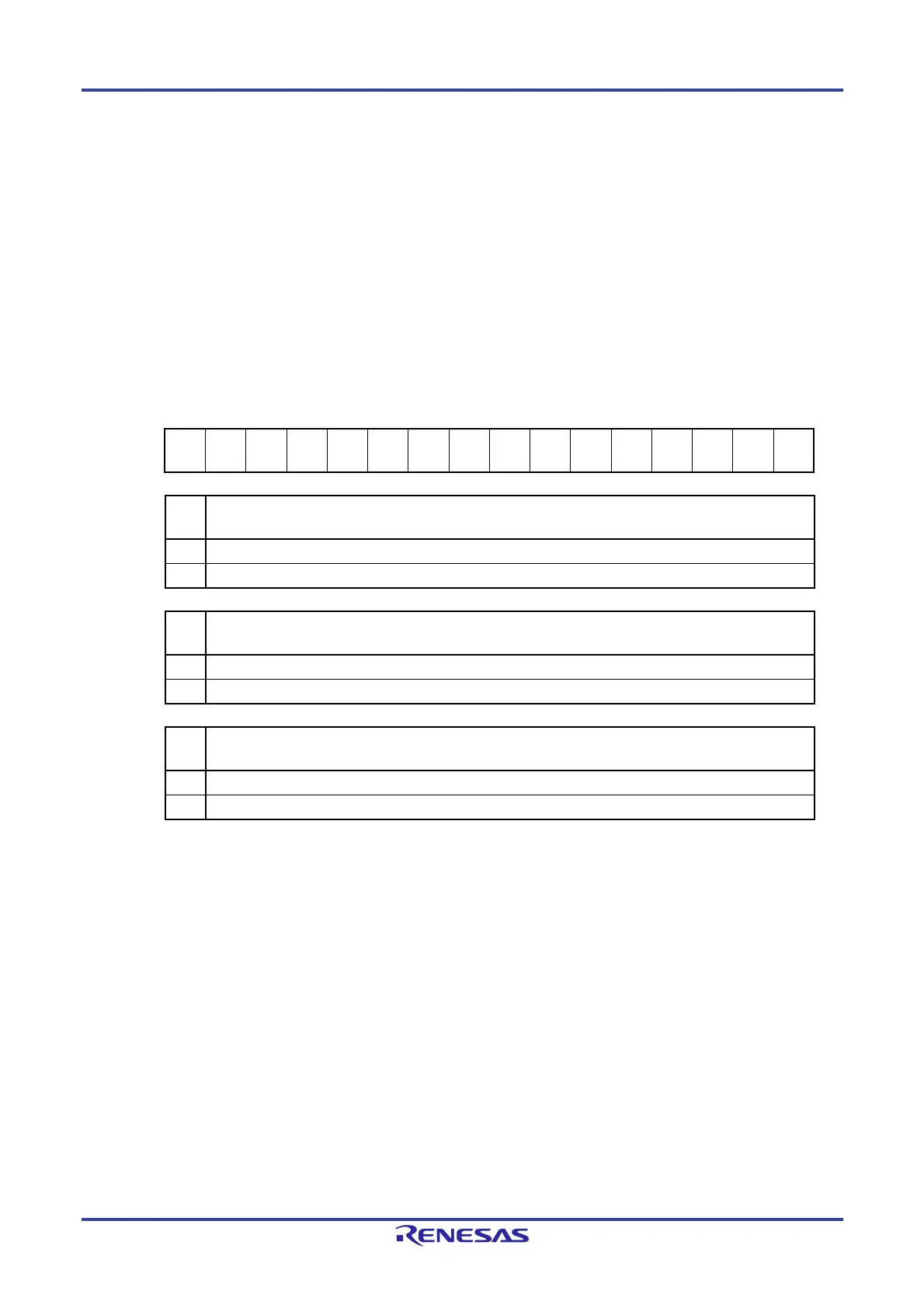

Figure 15-9. Format of Serial Flag Clear Trigger Register mn (SIRmn)

Address: F0104H, F0105H (SIR00), F0106H, F0107H (SIR01), After reset: 0000H R/W

F0144H, F0145H (SIR10), F0146H, F0147H (SIR11)

Symbol 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SIRmn 0 0 0 0 0 0 0 0 0 0 0 0 0

FECT

mn

PEC

Tmn

OVC

Tmn

FEC

Tmn

Clear trigger of framing error of channel n

0 Not cleared

1 Clears the FEFmn bit of the SSRmn register to 0.

PEC

Tmn

Clear trigger of parity error flag of channel n

0 Not cleared

1 Clears the PEFmn bit of the SSRmn register to 0.

OVC

Tmn

Clear trigger of overrun error flag of channel n

0 Not cleared

1 Clears the OVFmn bit of the SSRmn register to 0.

Cautions 1. Be sure to clear bits 15 to 3 to 0.

2. Use the SIRmn register to clear only the error flag set in the SSRn register. If the error flag not

set in this register is cleared, the flag may be erased when an error is detected from reading to

clearing this error flag.

Remarks 1. m: Unit number (m = 0, 1), n: Channel number (n = 0, 1)

2. When the SIRmn register is read, 0000H is always read.

3. If the clear trigger bit is set to 1 and the corresponding error flag is set to 1 at the same time, the error

flag setting is prioritized.

Loading...

Loading...