RL78/F13, F14 CHAPTER 5 CLOCK GENERATOR

R01UH0368EJ0210 Rev.2.10 392

Dec 10, 2015

4. When the clock monitor detects that the main system/PLL select clock has been

stopped, even if the SELPLL bit is set to 1 (SELPLL = 1), the clock through mode is

entered.

5. The counter for the lock-up wait time should be set to a period of at least 40 s.

6. When PLL operation starts, a wait time for the PLL to be locked is required.

7. When the PLL circuit is used, the PLL input clock and multiplication value can be set

only in the combinations shown in the following. When the PLL circuit is not used

(PLLON = 0 or SELPLL = 0), an input clock of any frequency between 1 to 32 MHz

can be selected.

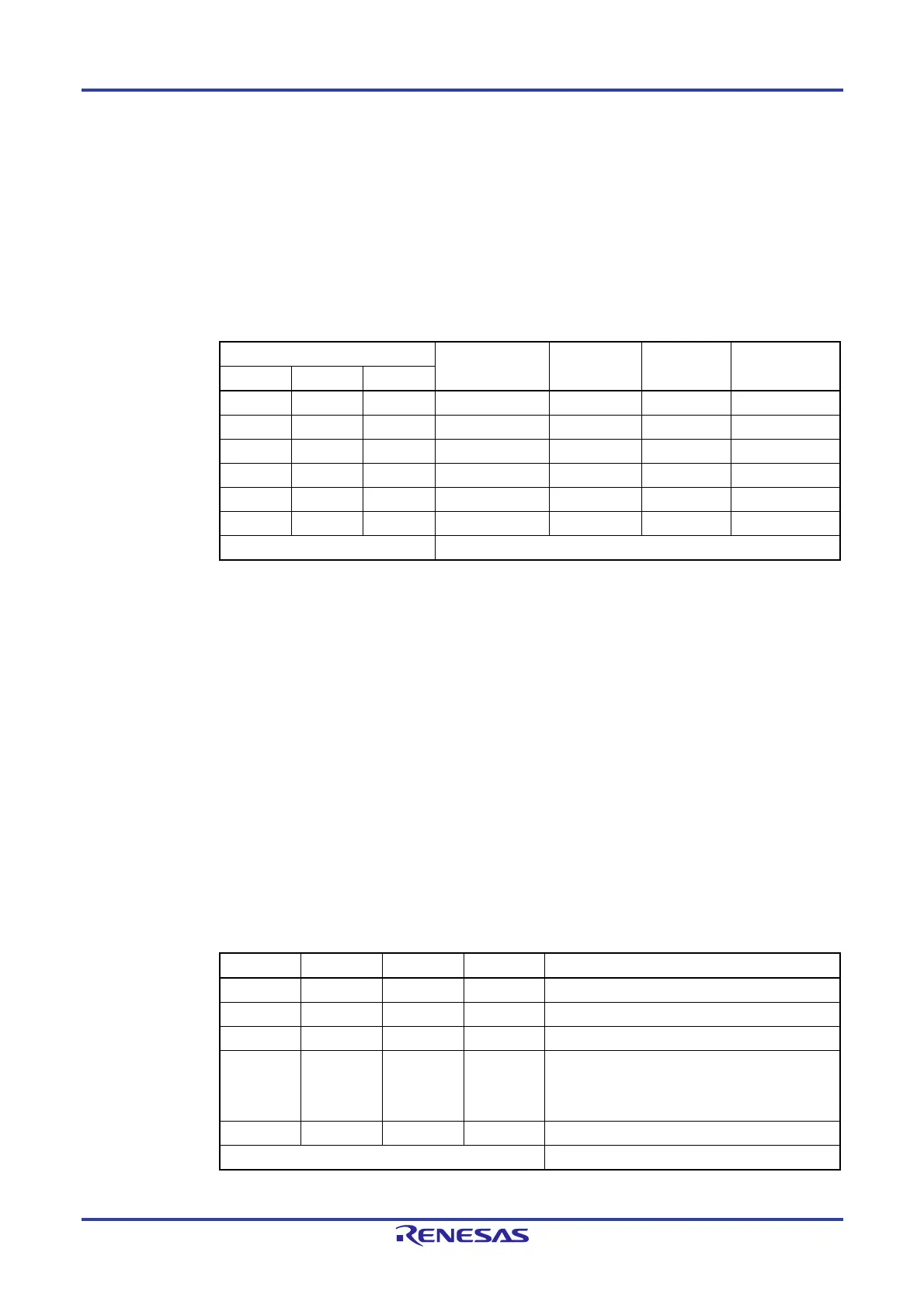

PLLCTL Register Inputtable

Frequency (fMAIN)

Multiplication Division Outputtable

Frequency (fPLL)

PLLMUL PLLDIV1 PLLDIV0

0 0 0 4MHz 2% 12 1/2 24MHz 2%

0 0 1 8MHz 2% 12 1/4 24MHz 2%

0 1 0 8MHz 2% 12 1/2 48MHz 2%

1 0 0 4MHz 2% 16 1/2 32MHz 2%

1 0 1 8MHz 2% 16 1/4 32MHz 2%

1 1 0 8MHz 2% 16 1/2 64MHz 2%

Other than above Setting prohibited

8. When PLLON = 0, simultaneously changing the PLLON bit and SELPLL bit through

8-bit access is disabled.

9. When the PLLON bit is cleared (becomes 0), the SELPLL bit is also automatically

cleared (clock through mode).

10. Before entering STOP mode, the PLLON bit should be cleared to 0.

11. Do not change the value of the MCM0 bit of the CKC register while the PLLON bit is

set to 1.

12. When FRQSEL4 = 1 in the user option byte (000C2H/020C2H), set the PLLDIV1 bit

to 0 (fPLL 32 MHz).

13. To change the SELPLL bit from 1 to 0 while PLLDIV1 = 1 (f

PLL > 32 MHz), stop counting

by the timer RD (setting the TSTART0 and TSTART1 bits in the TRDSTR register to

0) before changing the SELPLL bit.

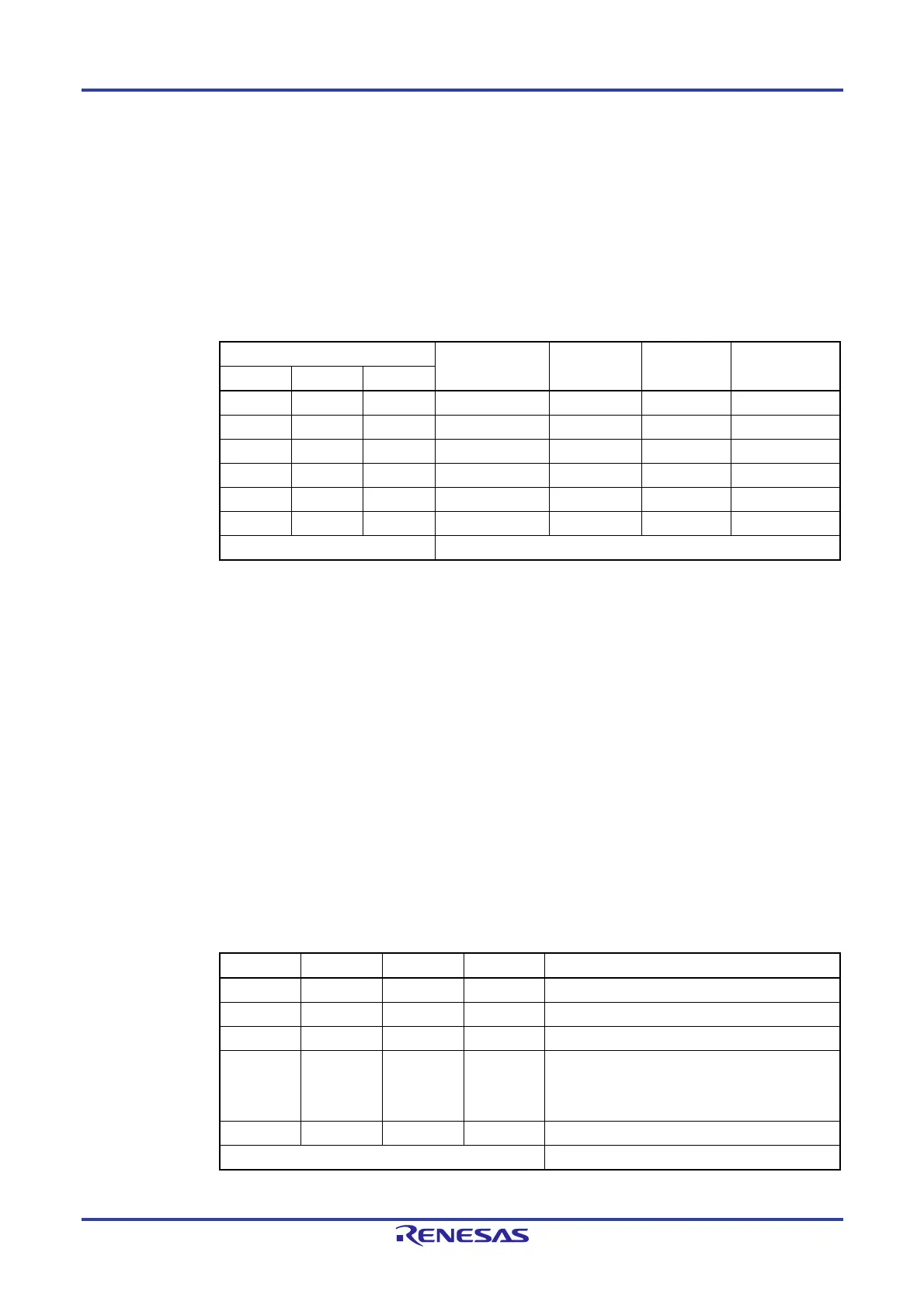

Remark When the PLLON and SELPLL bits are set, the clock selected for f

PLL is determined

according to the state of the LOCK and SELPLLS bits of the PLLSTS register. f

PLL for

each state of the PLLON, SELPLL, LOCK, and SELPLL bits is shown in the following.

PLLON SELPLL LOCK SELPLLS Selected Clock (fPLL)

0 0 0 0 Main system clock (fMAIN)

1 0 0 0 Main system clock (fMAIN)

1 0 1 0 Main system clock (fMAIN)

1 1 1 0 Main system clock (fMAIN)

State in which after the SELPLL bit is set to 1, the

clock has not switched to the multiplied clock.

1 1 1 1 PLL clock (fPLL)

Other than above Setting prohibited

Loading...

Loading...