RL78/F13, F14 CHAPTER 10 CLOCK OUTPUT/BUZZER OUTPUT CONTROLLER

R01UH0368EJ0210 Rev.2.10 689

Dec 10, 2015

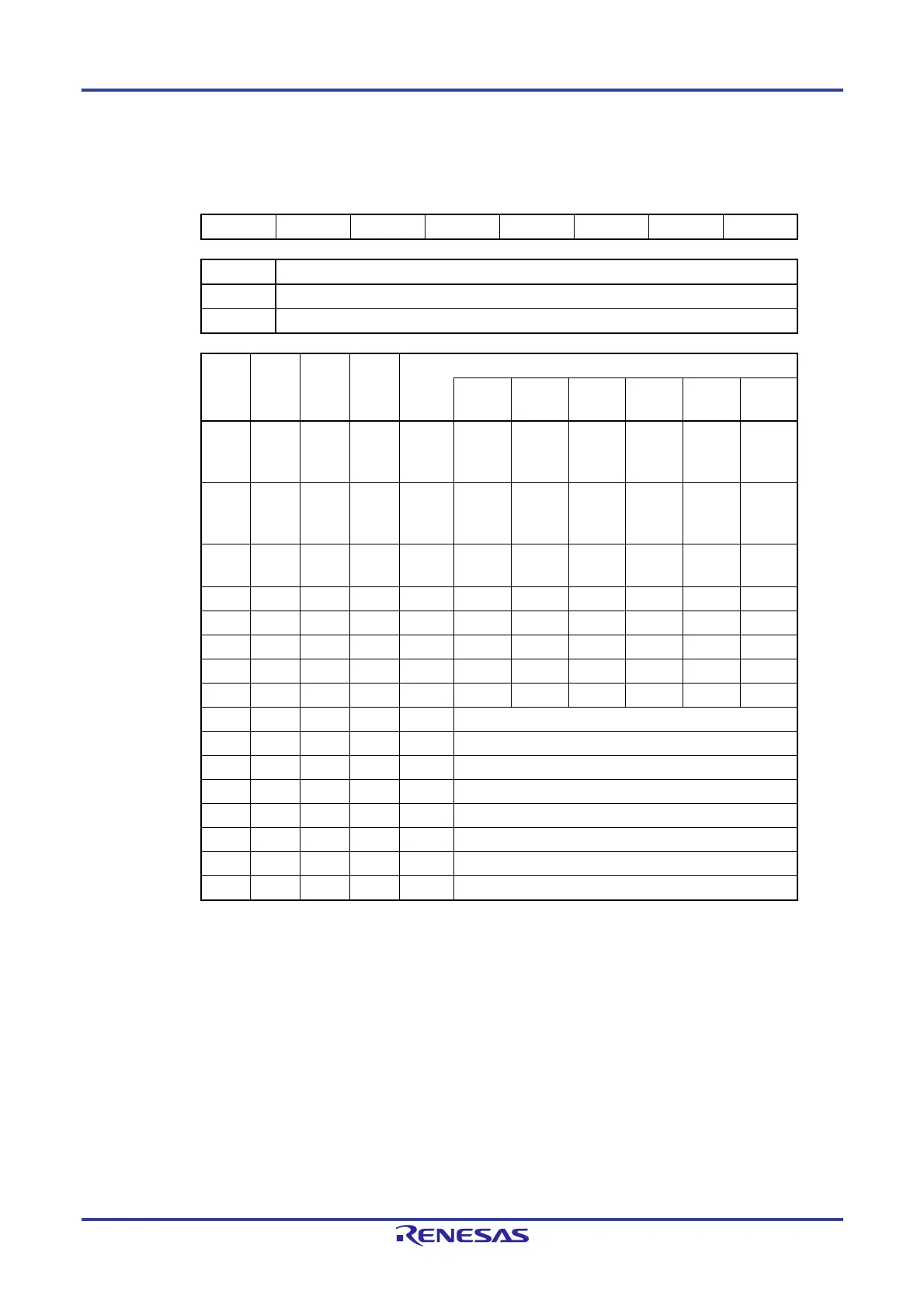

Figure 10-2. Format of Clock Output Select Register 0 (CKS0)

Address: FFFA5H (CKS0), FFFA6H (CKS1) After reset: 00H R/W

Symbol <7> 6 5 4 3 2 1 0

CKS0 PCLOE0 0 0 0 CSEL0 CCS02 CCS01 CCS00

PCLOE0 PCLBUZ0 pin output enable/disable specification

0 Output disable (default)

1 Output enable

CSEL0 CCS02 CCS01 CCS00 PCLBUZ0 pin output clock selection

f

MAIN =

5 MHz

fMAIN =

10 MHz

fMAIN =

20 MHz

fMAIN =

32 MHz

fMAIN =

48 MHz

fMAIN =

64 MHz

0 0 0 0 fMAIN 5 MHz

10 MHz

Note

Setting

prohibited

Note

Setting

prohibited

Note

Setting

prohibited

Note

Setting

prohibited

Note

0 0 0 1 fMAIN/2 2.5 MHz 5 MHz

10 MHz

Note

16 MHz

Note

Setting

prohibited

Note

Setting

prohibited

Note

0 0 1 0 fMAIN/2

2

1.25 MHz 2.5 MHz 5 MHz 8 MHz

12 MHz

Note

16 MHz

Note

0 0 1 1 fMAIN/2

3

625 kHz 1.25 MHz 2.5 MHz 4 MHz 6 MHz 8 MHz

0 1 0 0 fMAIN/2

4

312.5 kHz 625 kHz 1.25 MHz 2 MHz 3 MHz 4 MHz

0 1 0 1 fMAIN/2

11

2.44 kHz 4.88 kHz 9.76 kHz 15.62 kHz 23.43 kHz 31.25 kHz

0 1 1 0 fMAIN/2

12

1.22 kHz 2.44 kHz 4.88 kHz 7.81 kHz 11.71 kHz 15.12 kHz

0 1 1 1 fMAIN/2

13

610 Hz 1.22 kHz 2.44 kHz 3.90 kHz 5.85 kHz 7.81 kHz

1 0 0 0 fSL 32.768 kHz (fSUB) or 15 kHz (fIL)

1 0 0 1 fSL/2 16.384 kHz (fSUB) or 7.5 kHz (fIL)

1 0 1 0 fSL/2

2

8.192 kHz (fSUB) or 3.75 kHz (fIL)

1 0 1 1 fSL/2

3

4.096 kHz (fSUB) or 1.87 kHz (fIL)

1 1 0 0 fSL/2

4

2.048 kHz (fSUB) or 937.5 Hz (fIL)

1 1 0 1 fSL/2

5

1.024 kHz (fSUB) or 468.75 Hz (fIL)

1 1 1 0 fSL/2

6

512 Hz (fSUB) or 234.37 Hz (fIL)

1 1 1 1 fSL/2

7

256 Hz (fSUB) or 117.18 Hz (fIL)

Note Use the output clock within a range of 16 MHz. See the AC characteristics in CHAPTER 34 to CHAPTER 36

ELECTRICAL SPECIFICATIONS for details.

Cautions 1. Change the output clock and the CSEL0 and CCS02 to CCS00 bits after disabling clock output

(PCLOE0 = 0).

2. To shift to STOP mode when the main system clock is selected (CSEL0 = 0), set PCLOE0 = 0

before executing the STOP instruction. When the subsystem clock is selected (CSEL0 = 1),

PCLOE0 = 1 can be set because the clock can be output in STOP mode.

3. In the low-consumption RTC mode (when the RTCLPC bit of the operation speed mode control

register (OSMC) = 1), it is not possible to output the subsystem/low-speed on-chip oscillator

select clock (f

SL) from the PCLBUZ0 pin.

Loading...

Loading...