RL78/F13, F14 CHAPTER 3 CPU ARCHITECTURE

R01UH0368EJ0210 Rev.2.10 132

Dec 10, 2015

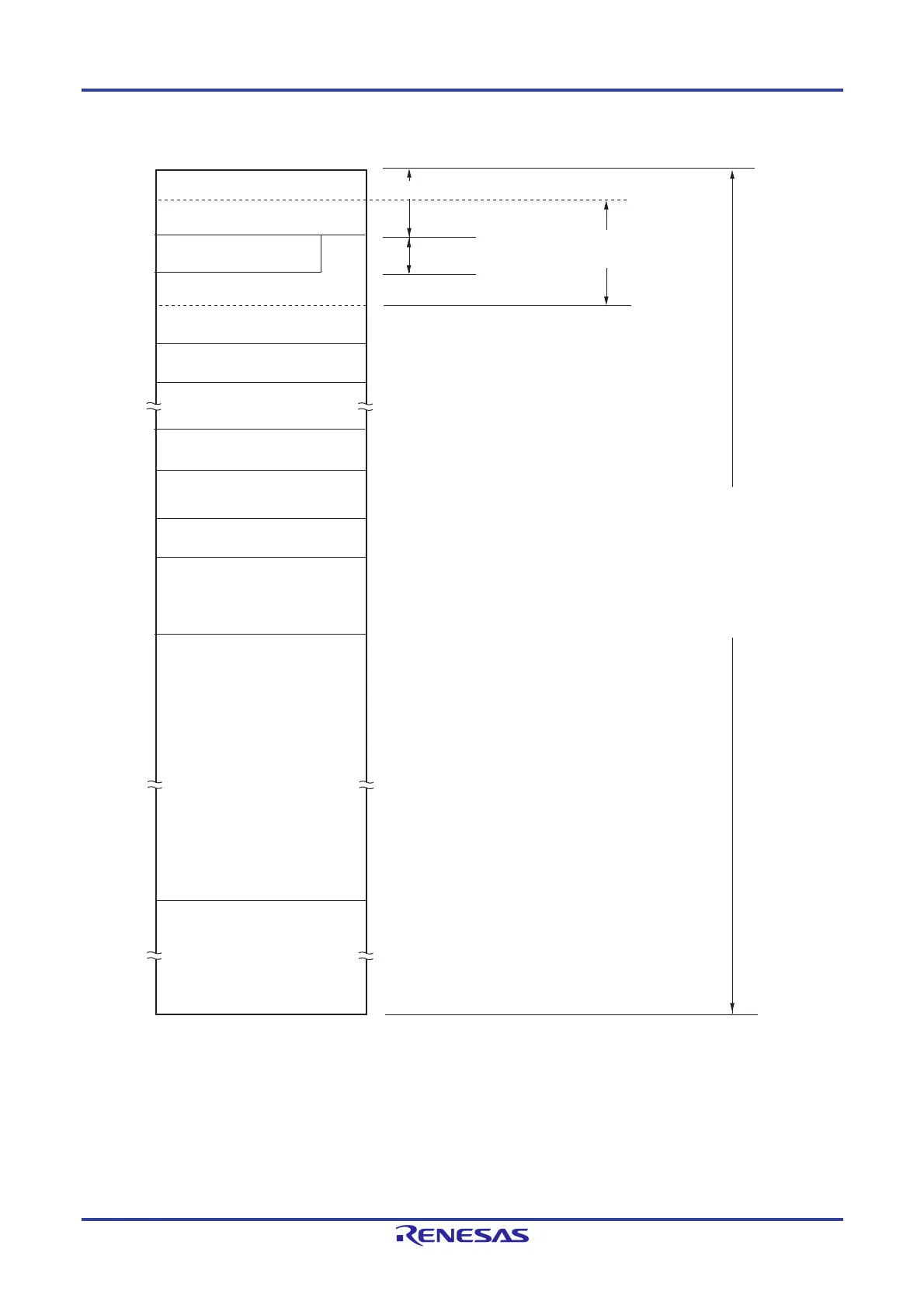

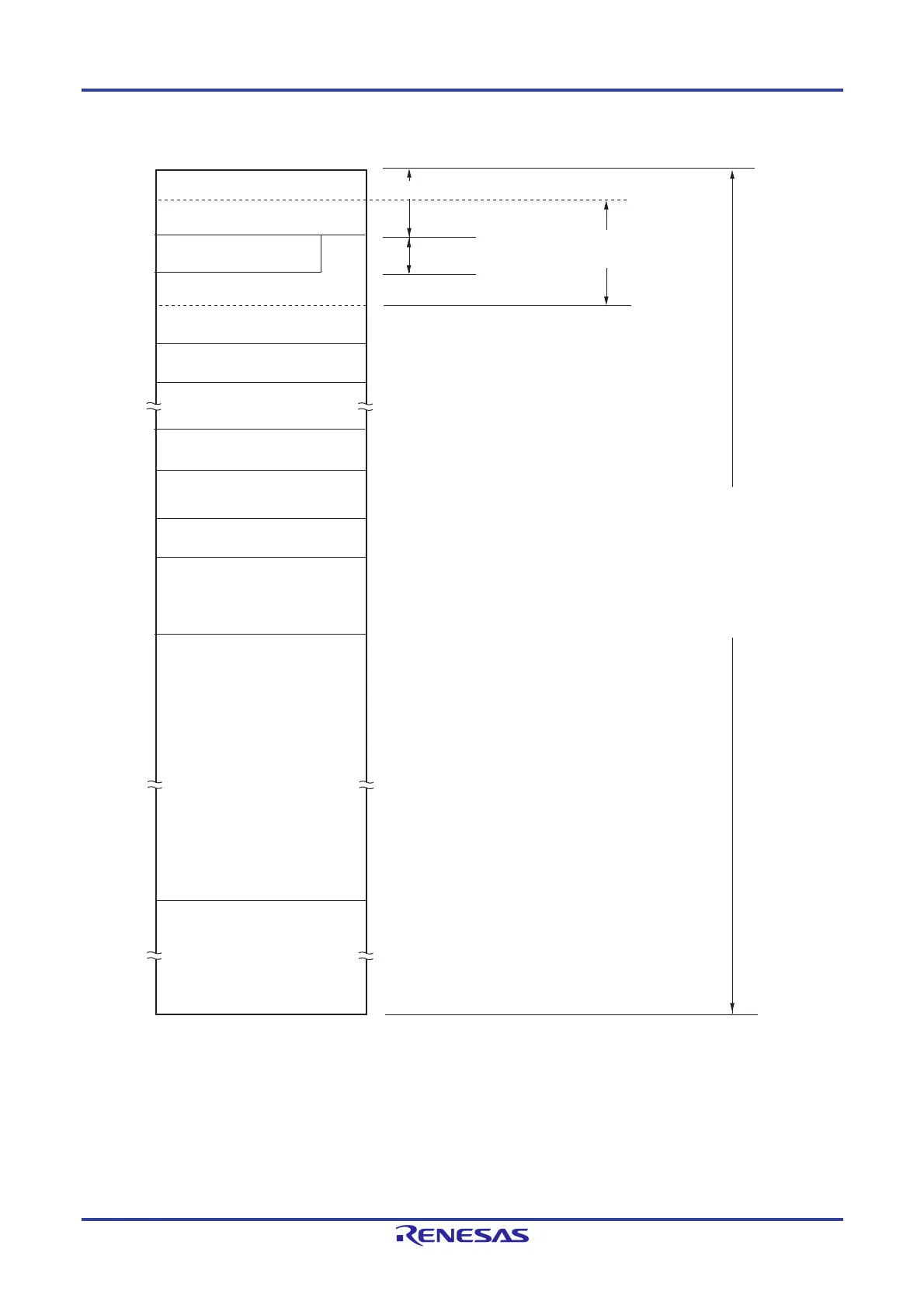

Figure 3-28. Correspondence between Data Memory and Addressing (R5F10PPE)

Caution When executing instructions from the RAM area, be sure to initialize the used RAM area + 10 bytes

with any desired value.

FFFFFH

00000H

FFF00H

FFEFFH

FFEE0H

FFEDFH

F0800H

F07FFH

F0000H

EFFFFH

10000H

0FFFFH

FAF00H

F

AEFFH

F3000H

F2FFFH

F1000H

F0FFFH

FFE20H

FFE1FH

FFF20H

FFF1FH

FE700H

FE6FFH

F2000H

F1FFFH

Special function register (SFR)

256 bytes

General-purpose register

32 bytes

Code flash memory

64 KB

Special function register (2nd SFR)

2 KB

Mirror

31.75 KB

Reserved

Reserved

Reserved

Reserved

Direct addressing

Register indirect addressing

Based addressing

Based indexed addressing

Short direct

addressing

SFR addressing

Register addressing

RAM

6 KB

Data flash memory

4 KB

Loading...

Loading...