RL78/F13, F14 CHAPTER 29 OPTION BYTE

R01UH0368EJ0210 Rev.2.10 1620

Dec 10, 2015

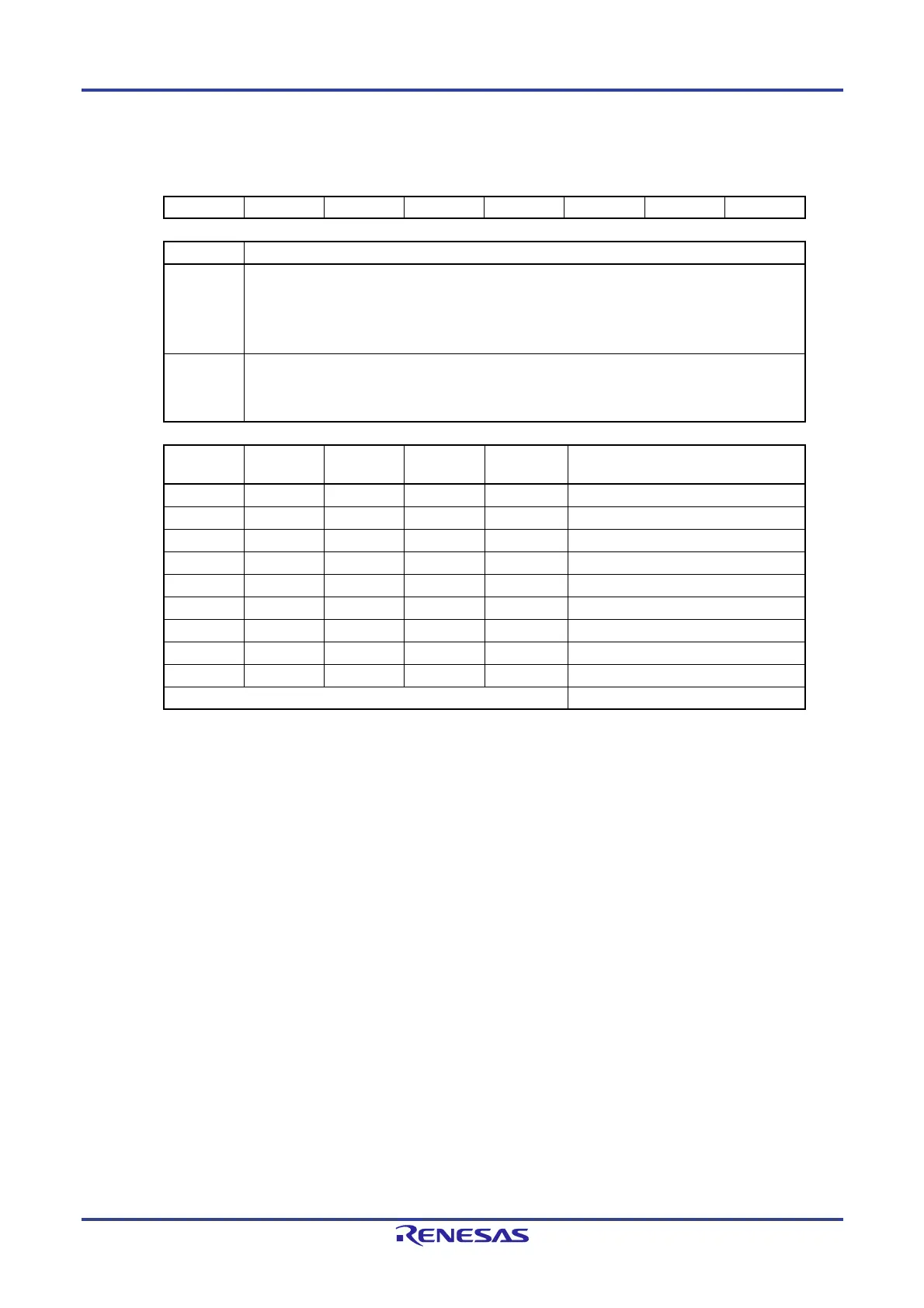

Figure 29-3. Format of Option Byte (000C2H/020C2H)

Address: 000C2H/020C2H

Note 1

After reset: (user setting value

Note 2

)

7 6 5 4 3 2 1 0

1 1 RESOUTB FRQSEL4 FRQSEL3 FRQSEL2 FRQSEL1 FRQSEL0

RESOUTB RESOUTB output function

0

Selects P130 as the RESOUT pin

• The low level is output during a reset.

• The high level is automatically output upon release from the reset state.

• The output latch value has no effect on the output.

1 Selects P130 as a general port pin (output only)

• The low level is output during a reset.

• The output latch value is output upon release from the reset state.

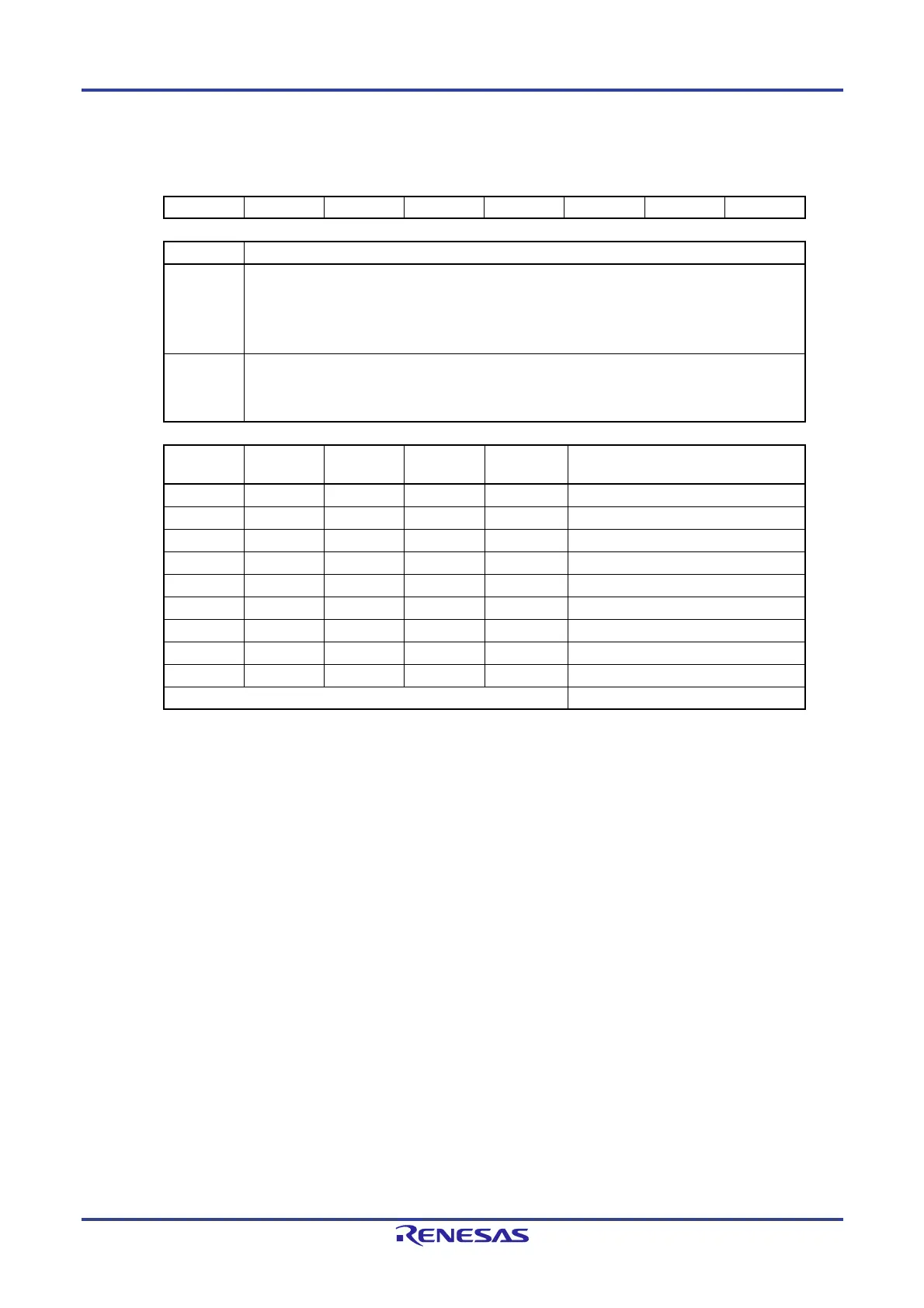

FRQSEL4 FRQSEL3 FRQSEL2 FRQSEL1 FRQSEL0 Frequency of the high-speed on-chip

oscillator clock

1 1 0 0 0

64 MHz

1 0 0 0 0

48 MHz

0 1 0 0 0

32 MHz

0 0 0 0 0

24 MHz

0 1 0 0 1

16 MHz

0 0 0 0 1

12 MHz

0 1 0 1 0

8 MHz

0 1 0 1 1

4 MHz

0 1 1 0 1

1 MHz

Other than above Setting prohibited

Notes 1. Set the same value as 000C2H to 020C2H when the boot swap operation is used because 000C2H is

replaced by 020C2H.

2. The setting at shipment of the user option byte is FFH.

Loading...

Loading...