RL78/F13, F14 CHAPTER 33 INSTRUCTION SET

R01UH0368EJ0210 Rev.2.10 1672

Dec 10, 2015

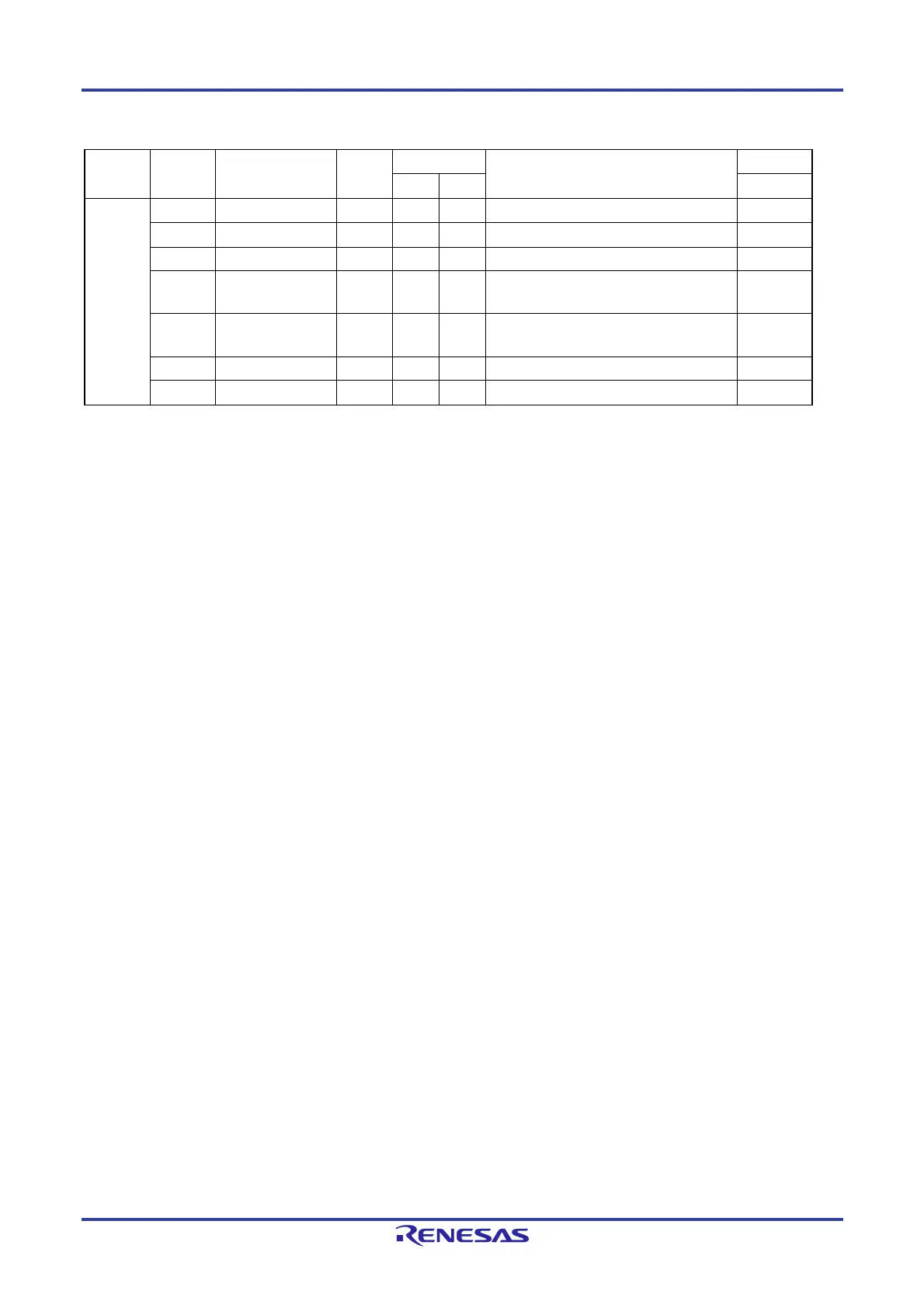

Table 33-5. Operation List (12/18)

Instruction

Group

Mnemonic Operands Bytes Clocks Operation Flag

Note 1 Note 2 Z AC CY

Multiply,

Divide,

Multiply &

accumu-

late

MULU X 1 1

AX A X

MULHU 3 2

BCAX AX BC (unsigned)

MULH 3 2

BCAX AX BC (signed)

DIVHU 3 9

AX (quotient), DE (remainder)

AX ÷ DE (unsigned)

DIVWU 3 17

BCAX (quotient), HLDE (remainder)

BCAX ÷ HLDE (unsigned)

MACHU 3 3

MACR MACR + AX BC (unsigned)

MACH 3 3

MACR MACR + AX BC(signed)

Notes 1. Number of CPU clocks (fCLK) when the internal RAM area, SFR area, or extended SFR area is accessed, or

when no data is accessed.

2. Number of CPU clocks (f

CLK) when the program memory area is accessed.

Caution Disable interrupts when executing the DIVHU or DIVWU instruction in an interrupt servicing routine.

Alternatively, unless they are executed in the RAM area, note that execution of a DIVHU or DIVWU

instruction is possible even with interrupts enabled as long as a NOP instruction is added immediately

after the DIVHU or DIVWU instruction in the assembly language source code. The following compilers

automatically add a NOP instruction immediately after any DIVHU or DIVWU instruction output during the

build process.

- V. 1.71 and later versions of the CA78K0R (Renesas Electronics compiler), for both C and assembly

language source code

- Service pack 1.40.6 and later versions of the EWRL78 (IAR compiler), for C language source code

- GNURL78 (KPIT compiler), for C language source code

Remarks 1. Number of clock is when program exists in the internal ROM (flash memory) area. If fetching the instruction

from the internal RAM area, the number becomes double number plus 3 clocks at a maximum.

2. MACR indicates the multiplication and accumulation register (MACRH, MACRL).

<R>

Loading...

Loading...