RL78/F13, F14 CHAPTER 4 PORT FUNCTIONS

R01UH0368EJ0210 Rev.2.10 355

Dec 10, 2015

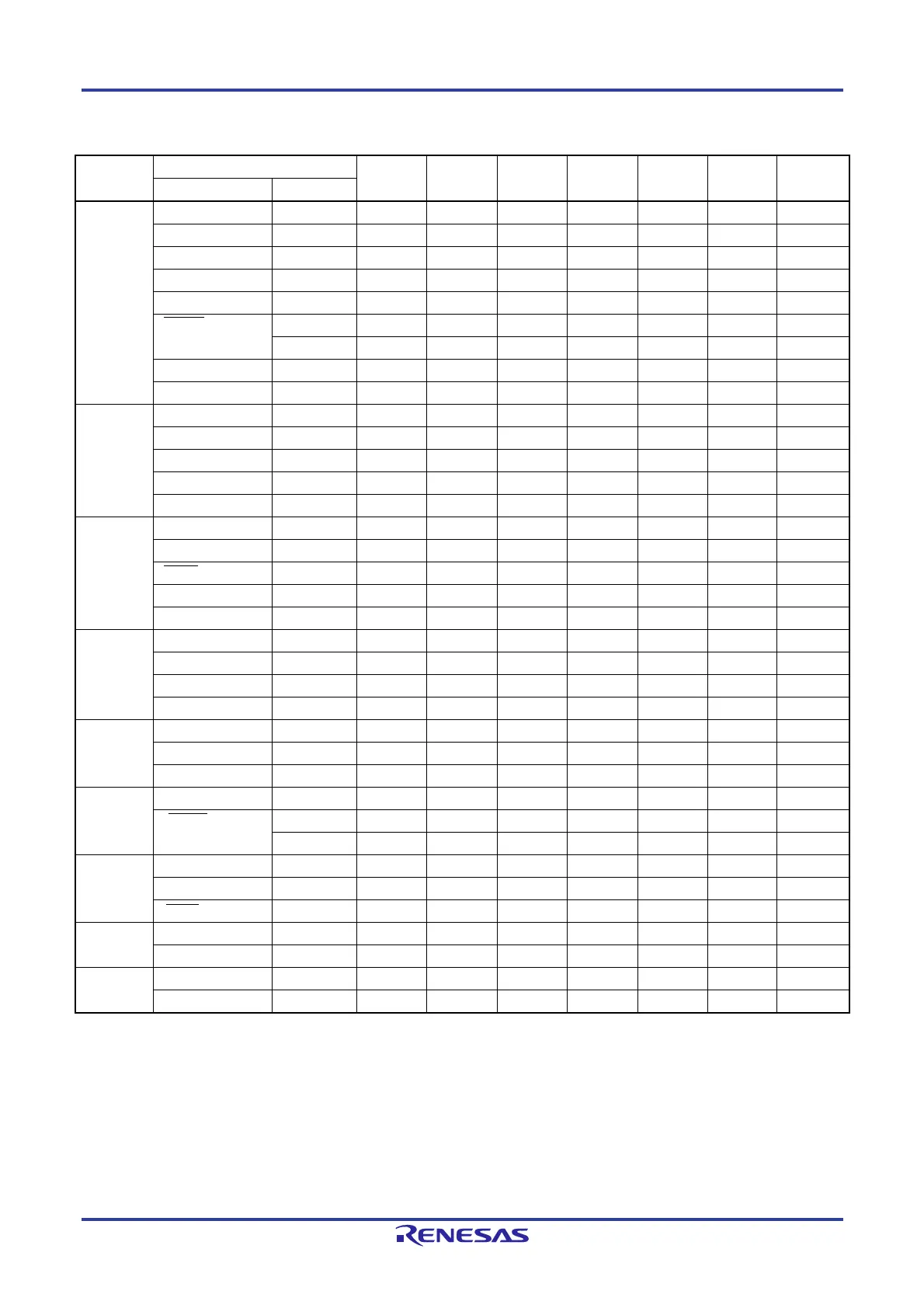

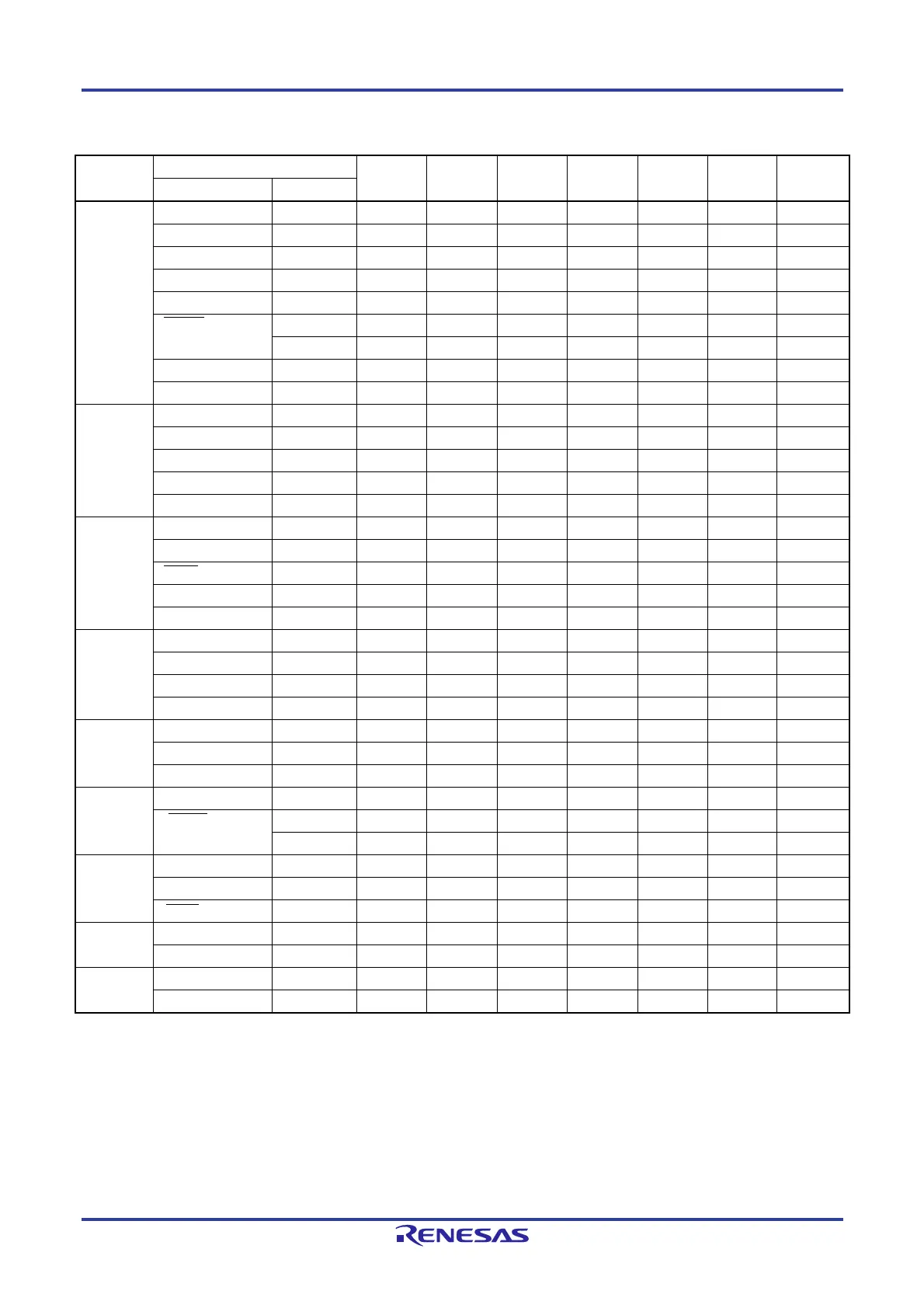

Table 4-29. Settings of Port Mode Register and Output Latch When Using Alternate Function (6/8)

Pin Name Alternate Function PIORXX POMXX PMCXX PMXX PXX PIMXX PITHLXX

Function Name I/O

P71 ANI27 Input × × 1 1 × × ×

TI17 Input 0 × 0 1 × 0 0/1

INTP6 Input × × 0 1 × 0 0/1

TO17 Output 0 0 0 0 0 × ×

KR1 Input 0 × 0 1 × 0 0/1

SCK11 Input 0 × 0 1 × 0/1 0/1

Output 0 0/1 0 0 1 × ×

SCL11 Output 0 0/1 0 0 1 × ×

SNZOUT5 Output 0 0 0 0 0 × ×

P72 ANI28 Input × × 1 1 × – –

KR2 Input 0 × 0 1 × – –

SO11 Output 0 0/1 0 0 1 – –

SNZOUT6 Output 0 0 0 0 0 – –

(CTXD0) Output 1 0 0 0 1 – –

P73 ANI29 Input × – 1 1 × × ×

KR3 Input 0 – 0 1 × 0 0/1

SSI11 Input 0 – 0 1 × 0/1 0/1

SNZOUT7 Output 0 – 0 0 0 × ×

(CRXD0) Input 1 – 0 1 × 0 0/1

P74 ANI30 Input × – 1 1 × – –

KR4 Input 0 – 0 1 × – –

(SO10) Output 1 – 0 0 1 – –

(TXD1) Output 1 – 0 0 1 – –

P75 KR5 Input 0 – – 1 × – 0/1

(SI10) Input 1 – – 1 × – 0/1

(RXD1) Input 1 – – 1 × – 0/1

P76 KR6 Input 0 – – 1 × – 0/1

(SCK10) Input 1 – – 1 × – 0/1

Output 1 – – 0 1 – ×

P77 INTP12 Input × – – 1 × – 0/1

KR7 Input 0 – – 1 × – 0/1

(SSI10) Input 1 – – 1 × – 0/1

P80 ANI02 Input × – – 1 × – –

ANO0 Output × – – 1 × – –

P81 ANI03 Input × – – 1 × – –

IVCMP00 Input × – – 1 × – –

Remarks 1. : Don't care

PIORxx: Peripheral I/O redirection register

POMxx: Port output mode register

PMCxx: Port mode control register

PMxx: Port mode register

Pxx: Port output latch

2. The relationship between pins and their alternate functions shown in this table indicates the relationship

when a 100-pin product is used. In other products, alternate functions might be assigned to different

pins, but even in this case, the PIORxx, POMxx, PMCxx, PMxx, and Pxx set in the same way.

Loading...

Loading...