RL78/F13, F14 CHAPTER 8 TIMER RD

R01UH0368EJ0210 Rev.2.10 617

Dec 10, 2015

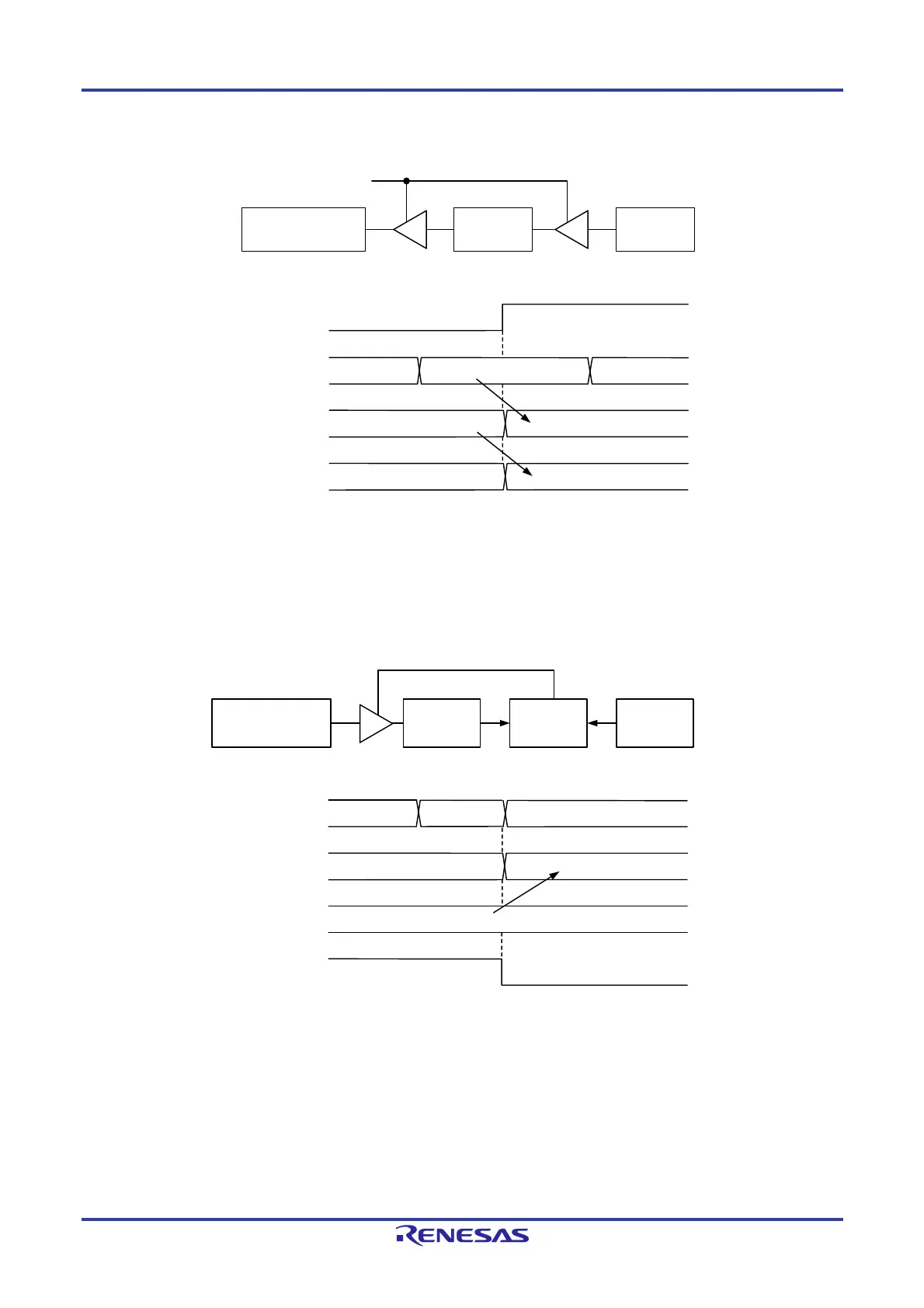

Figure 8-41. Buffer Operation in Input Capture Function

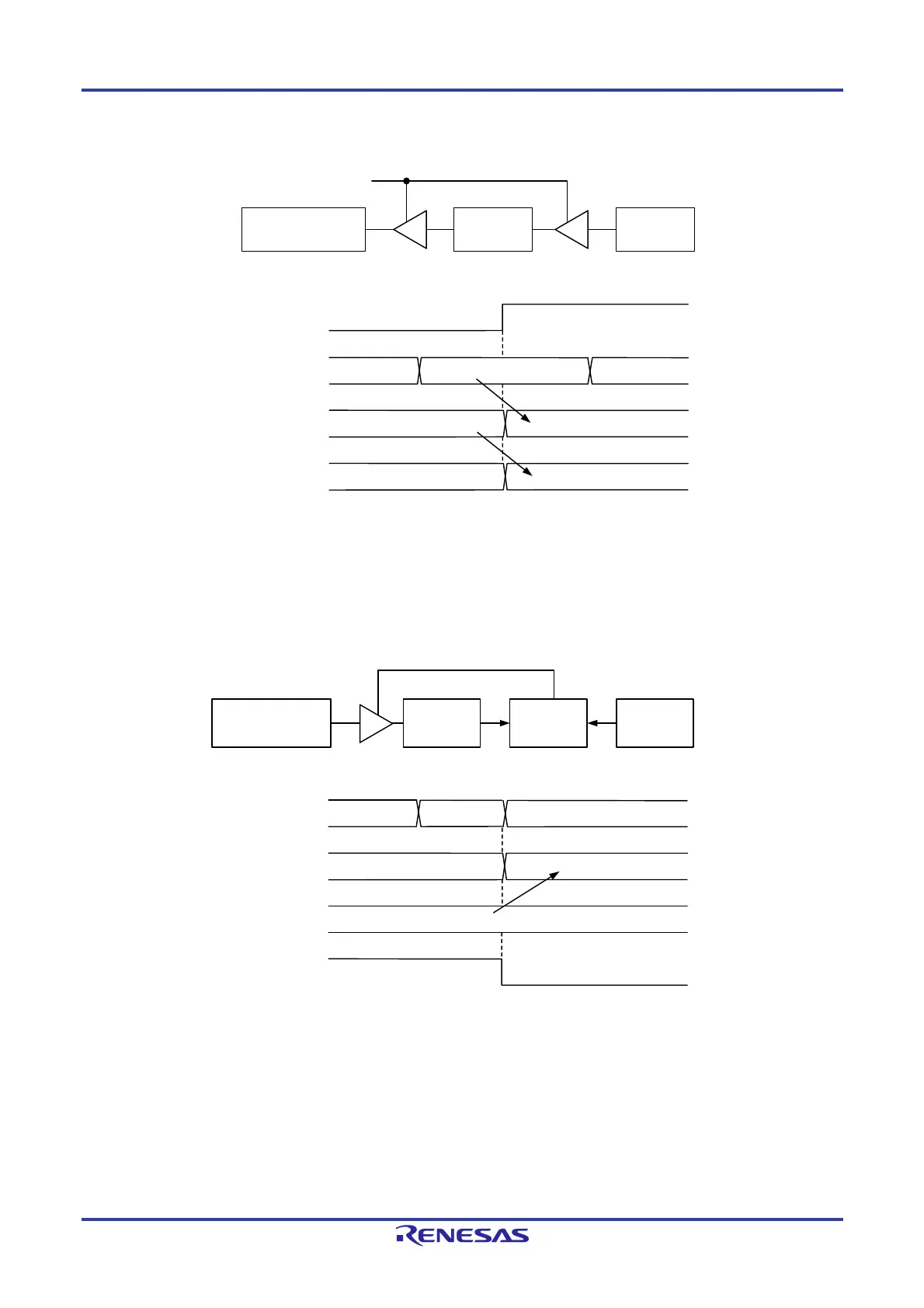

Figure 8-42. Buffer Operation in Output Compare Function

m

Transfer

n

n - 1

n + 1

m

Transfer

n

TRDi

TRDIOAi input

(input capture signal)

TRDGRCi register

(buffer)

TRDGRAi

register

TRDIOAi input

TRDi register

TRDGRAi register

TRDGRCi register

(buffer)

Remark

i = 0 or 1

The above diagram applies under the following conditions:

• The TRDBFCi bit in the TRDMR register is set to 1 (TRDGRCi register is buffer register for TRDGRAi register).

• Bits IOA2 to IOA0 in the TRDIORAi register are set to 100B (input capture at the rising edge).

mn

m + 1

n

Transfer

Comparator TRDi

Compare match signal

m - 1

m

Remark

i = 0 or 1

The above diagram applies under the following conditions:

• The TRDBFCi bit in the TRDMR register is set to 1 (TRDGRCi register is buffer register for TRDGRAi register).

• Bits IOA2 to IOA0 in the TRDIORAi register are set to 001B (low output by compare match).

TRDi register

TRDGRAi register

TRDGRCi register

(buffer)

TRDIOAi output

TRDGRCi register

(buffer)

TRDGRAi

register

Loading...

Loading...