RL78/F13, F14 CHAPTER 15 SERIAL ARRAY UNIT

R01UH0368EJ0210 Rev.2.10 973

Dec 10, 2015

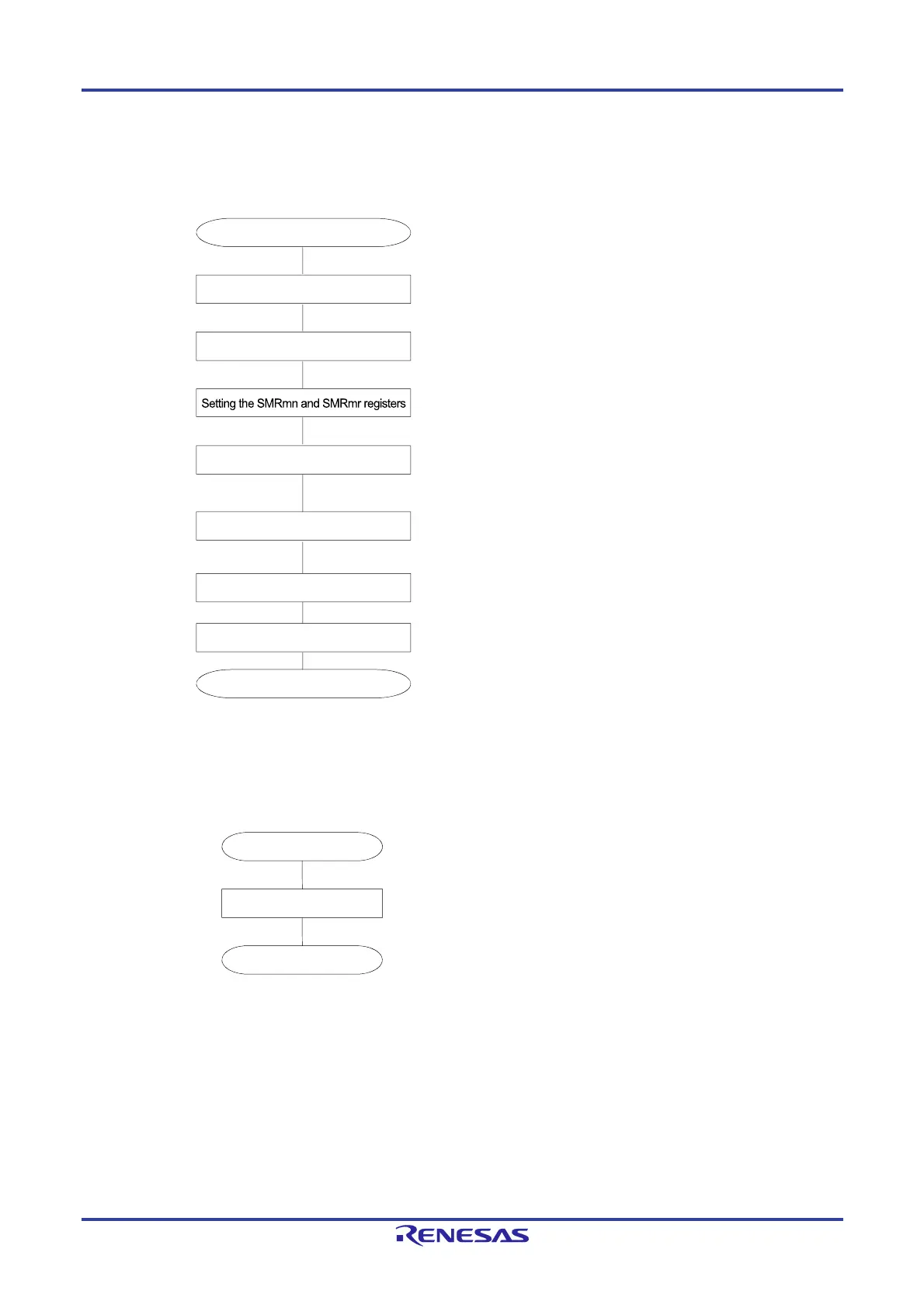

(2) Operation procedure

Figure 15-130. Initial Setting Procedure for UART Reception

Caution For the UART reception, set the RXEmn bit of SCRmn register to 1, and then be sure to set SSmn

to 1 after 4 or more fMCK clocks have elapsed.

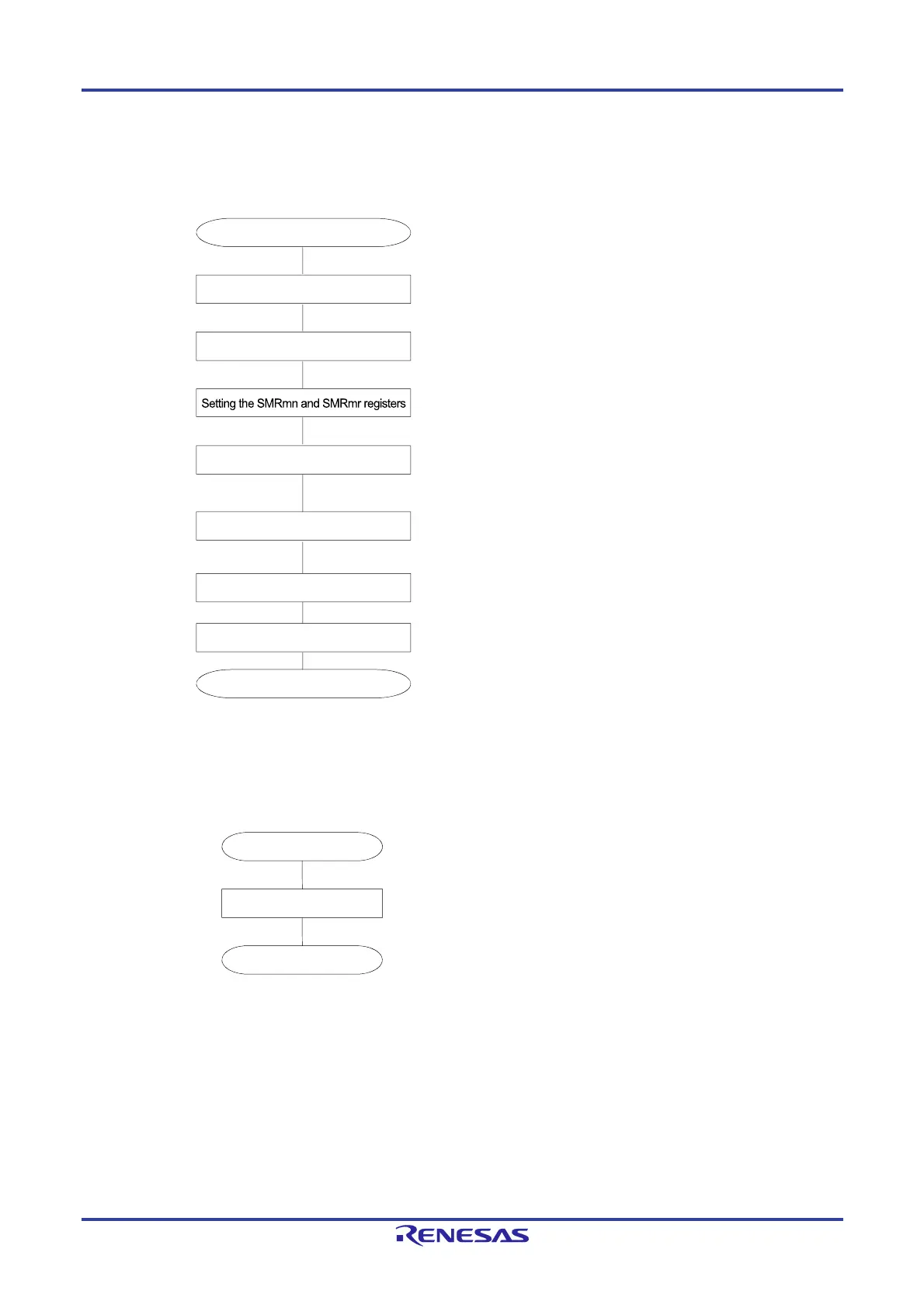

Figure 15-131. Procedure for Stopping UART Reception

Remark m: Unit number (m = 0, 1), n: Channel number (n = 1), mn = 00, 10, r: Channel number (r = n − 1)

Starting initial setting

Setting the PER0 register

Setting the SPSm register

Setting the SCRmn register

Setting the SDRmn register

Writing to the SSm register

Starting communication

Release the serial array unit from the

reset status and start clock supply.

Set the operation clock.

Set an operation mode, etc.

Set a communication format.

e

a

rans

er

au

ra

e

se

ng

e

transfer clock by dividing the operation

clock (fMCK)).

e

e

mn

o

e

arge

c

anne

o

an

set the SEmn bit to 1 (to enable operation).

The start bit is detected.

Setting port

Enable data input of the target channel

by setting a port register and a port

mode register.

Starting setting to stop

Setting the STm register

Stopping communication

Write 1 to the STmn bit of the target

channel.

Stop communication in midway.

Loading...

Loading...