RL78/F13, F14 CHAPTER 21 INTERRUPT FUNCTIONS

R01UH0368EJ0210 Rev.2.10 1490

Dec 10, 2015

21.3.1 Interrupt request flag registers (IF0L, IF0H, IF1L, IF1H, IF2L, IF2H, IF3L)

The interrupt request flags are set to 1 when the corresponding interrupt request is generated or an instruction is executed.

They are cleared to 0 when an instruction is executed upon acknowledgment of an interrupt request or upon reset signal

generation.

When an interrupt is acknowledged, the interrupt request flag is automatically cleared and then the interrupt routine is

entered.

The IF0L, IF0H, IF1L, IF1H, IF2L, IF2H, and IF3L registers can be set by a 1-bit or 8-bit memory manipulation instruction.

When the IF0L and IF0H registers, the IF1L and IF1H registers, and the IF2L and IF2H registers are combined to form 16-

bit registers IF0, IF1, and IF2, they can be set by a 16-bit memory manipulation instruction.

Reset signal generation clears these registers to 00H.

Remark If an instruction that writes data to this register is executed, the number of instruction execution clocks

increases by 2 clocks.

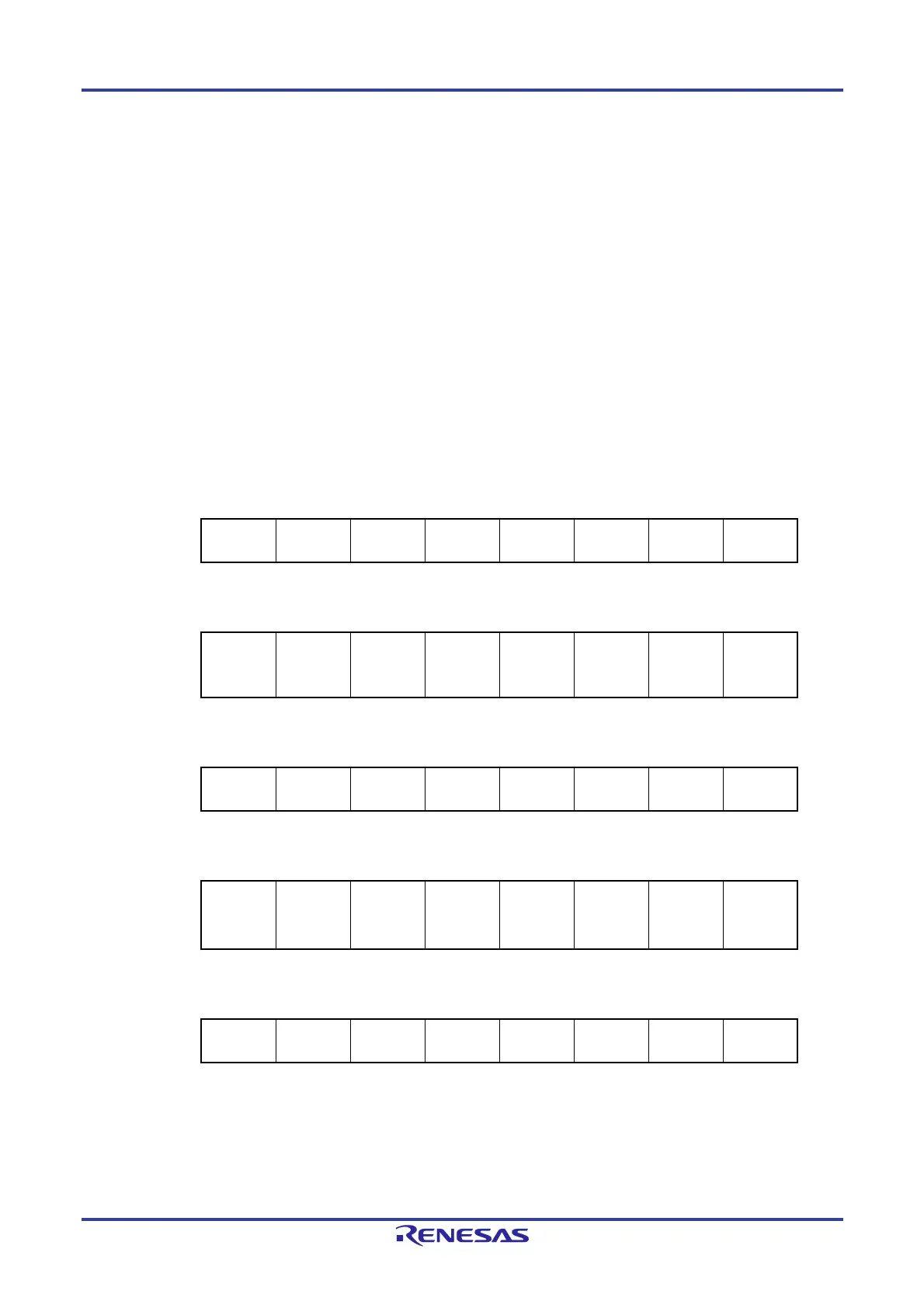

Figure 21-2. Format of Interrupt Request Flag Registers (IF0L, IF0H, IF1L, IF1H, IF2L, IF2H, IF3L) (1/2)

ddress: FFFE0H After reset: 00H R/W

Symbol <7> <6> <5> <4> <3> <2> <1> <0>

IF0L

PIF5

CMPIF0

PIF4

SPMIF

PIF3 PIF2 PIF1 PIF0 LVIIF WDTIIF

ddress: FFFE1H After reset: 00H R/W

Symbol <7> <6> <5> <4> <3> <2> <1> <0>

IF0H LIN0TRMIF RAMIF TRJIIF0 TRDIF1 TRDIF0 SRIF0

CSIIF01

IICIF01

STIF0

CSIIF00

IICIF00

CLMIF

PIF13

ddress: FFFE2H After reset: 00H R/W

Symbol <7> <6> <5> <4> <3> <2> <1> <0>

IF1L TMIF03 TMIF02 TMIF01 TMIF00

PIF8

RTCIF

IICAIF0

LIN0STAIF

LIN0IF

LIN0RVCIF

ddress: FFFE3H After reset: 00H R/W

Symbol <7> <6> <5> <4> <3> <2> <1> <0>

IF1H TMIF04

SRIF1

CSIIF11

IICIF11

STIF1

CSIIF10

IICIF10

PIF10

TMIF03H

PIF9

TMIF01H

PIF7

TMIF13H

PIF6

TMIF11H

ADIF

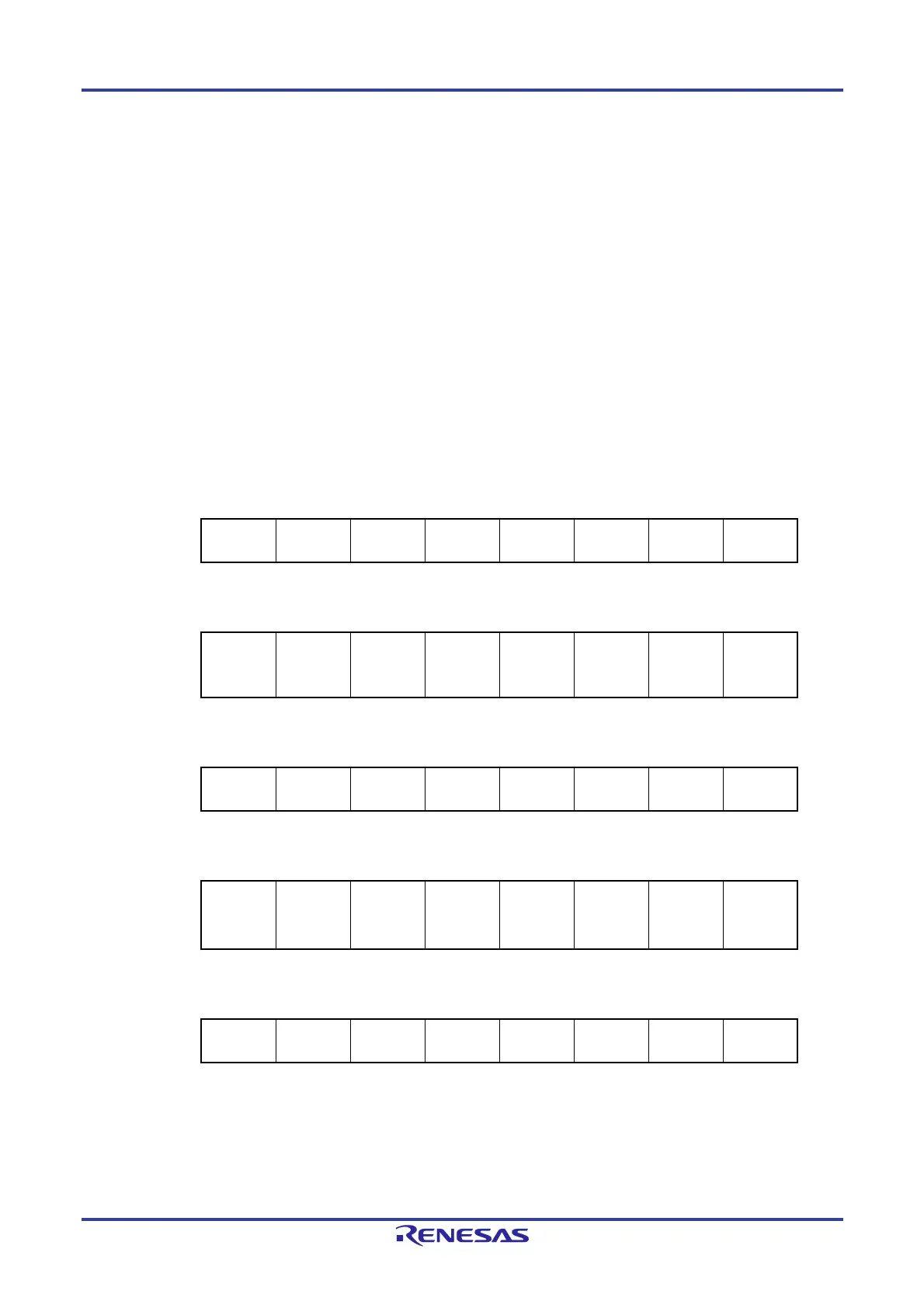

ddress: FFFD0H After reset: 00H R/W

Symbol <7> <6> <5> <4> <3> <2> <1> <0>

IF2L CAN0CFRIF CAN0WUPIF CAN0ERRIF KRIF

PIF11

LIN0WUPIF

TMIF07 TMIF06 TMIF05

Loading...

Loading...