RL78/F13, F14 CHAPTER 18 CAN INTERFACE (RS-CAN LITE)

R01UH0368EJ0210 Rev.2.10 1286

Dec 10, 2015

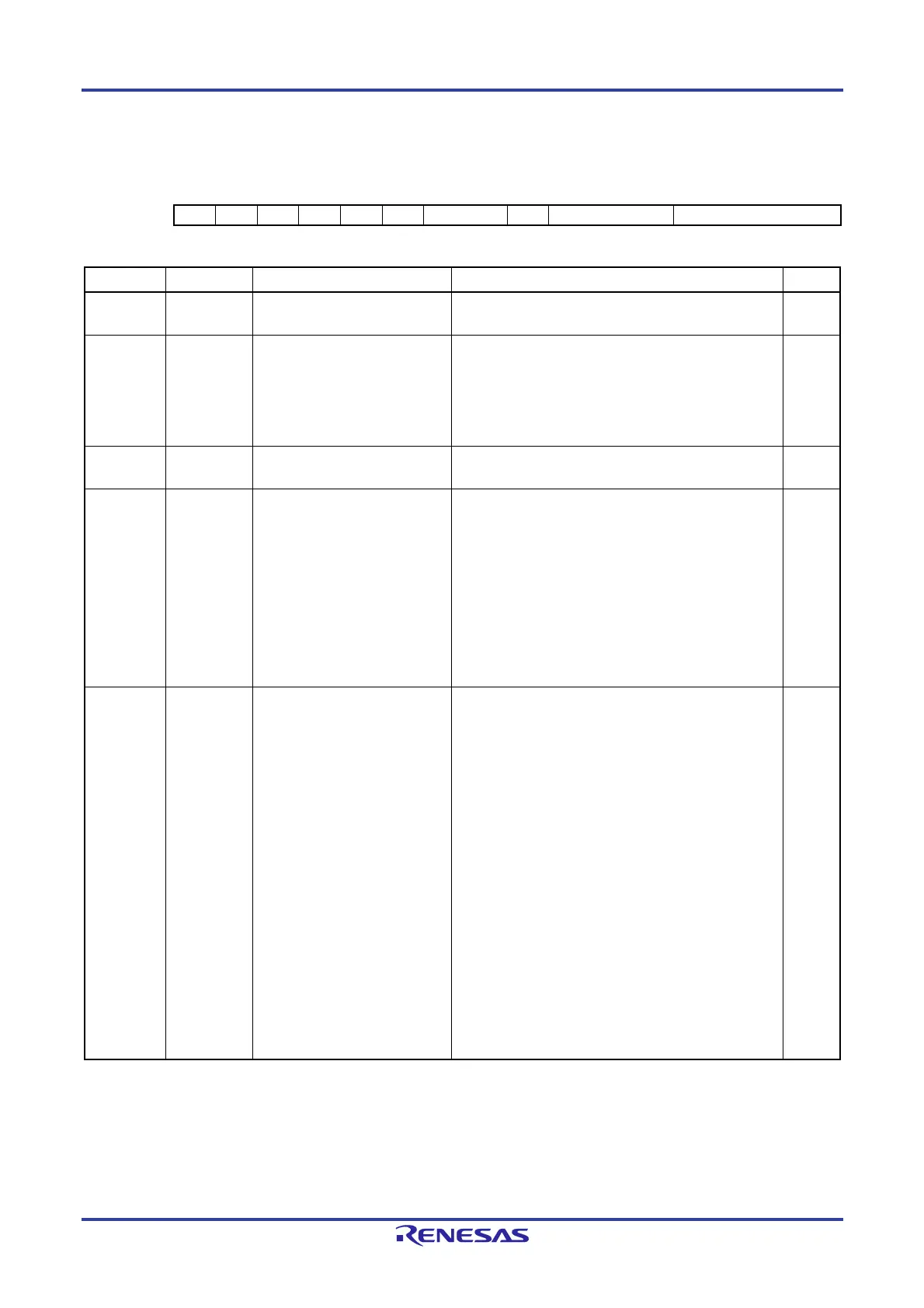

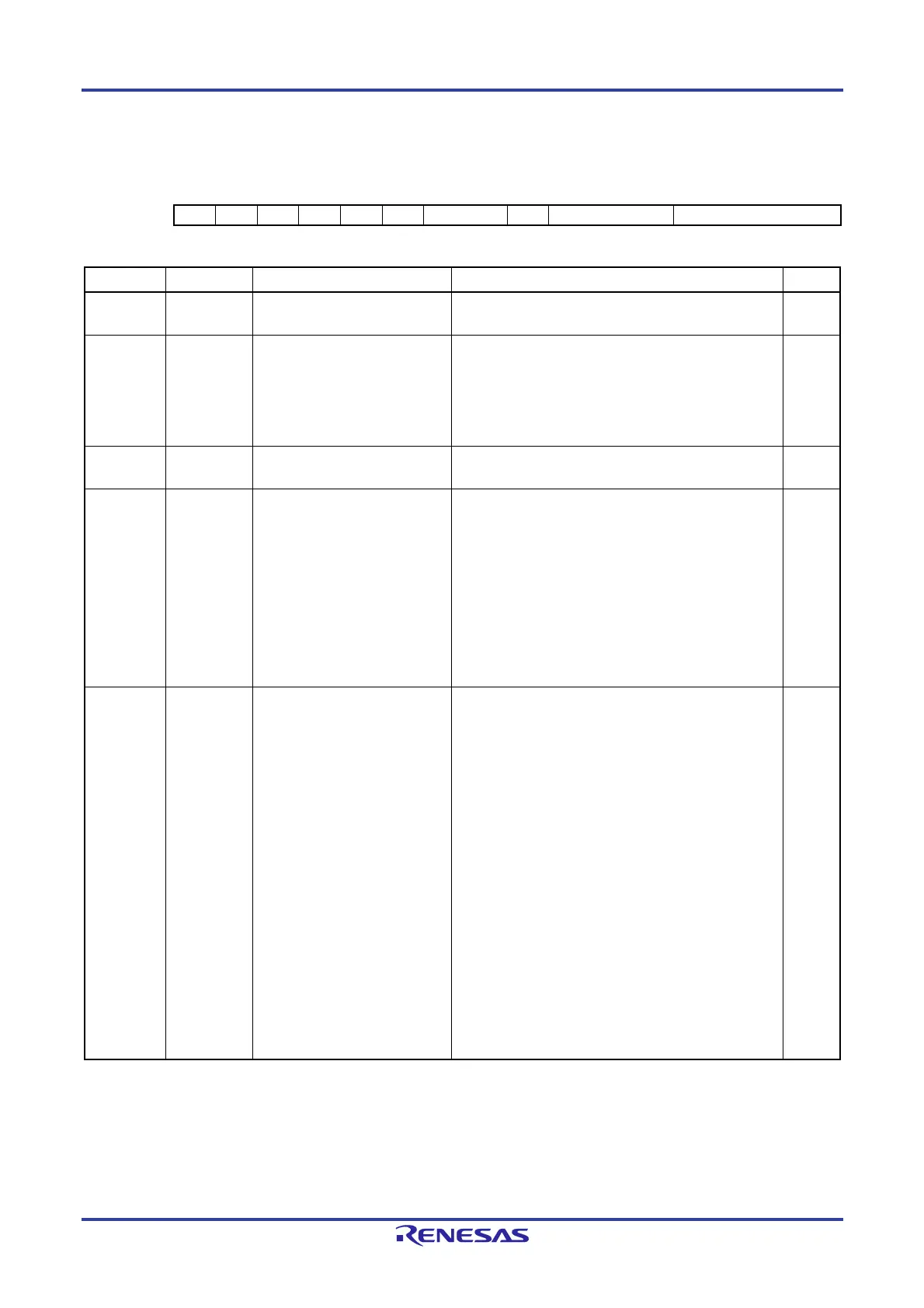

18.3.2 CANi Bit Configuration Register H (CiCFGH) (i = 0)

Address C0CFGHL: F0302H, C0CFGHH: F0303H

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

— — — — — — SJW[1:0] — TSEG2[2:0] TSEG1[3:0]

After Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bit Symbol Bit Name Description R/W

15 to 10 — Reserved

These bits are always read as 0. The write value

should always be 0.

R

9, 8 SJW[1:0]

Resynchronization Jump

Width Control

b9 b8

0 0 : 1 Tq

0 1 : 2 Tq

1 0 : 3 Tq

1 1 : 4 Tq

R/W

7 — Reserved

This bit is always read as 0. The write value should

always be 0.

R

6 to 4

TSEG2

[2:0]

Time Segment 2 Control

b6 b5 b4

0 0 0 : Setting prohibited

0 0 1 : 2 Tq

0 1 0 : 3 Tq

0 1 1 : 4 Tq

1 0 0 : 5 Tq

1 0 1 : 6 Tq

1 1 0 : 7 Tq

1 1 1 : 8 Tq

R/W

3 to 0

TSEG1

[3:0]

Time Segment 1 Control

b3 b2 b1 b0

0 0 0 0 : Setting prohibited

0 0 0 1 : Setting prohibited

0 0 1 0 : Setting prohibited

0 0 1 1 : 4 Tq

0 1 0 0 : 5 Tq

0 1 0 1 : 6 Tq

0 1 1 0 : 7 Tq

0 1 1 1 : 8 Tq

1 0 0 0 : 9 Tq

1 0 0 1 : 10 Tq

1 0 1 0 : 11 Tq

1 0 1 1 : 12 Tq

1 1 0 0 : 13 Tq

1 1 0 1 : 14 Tq

1 1 1 0 : 15 Tq

1 1 1 1 : 16 Tq

R/W

Modify the CiCFGH register only in channel reset mode or channel halt mode. Set this register in channel reset mode

before making a transition to channel communication mode or channel halt mode. For setting bit timing, see 18.10 Initial

Settings.

Loading...

Loading...