RL78/F13, F14 CHAPTER 18 CAN INTERFACE (RS-CAN LITE)

R01UH0368EJ0210 Rev.2.10 1357

Dec 10, 2015

18.3.61 CANi Transmit Buffer Control Register p (TMCp) (i = 0) (p = 0 to 3)

Address TMC0: F0364H, TMC1: F0365H

TMC2: F0366H, TMC3: F0367H

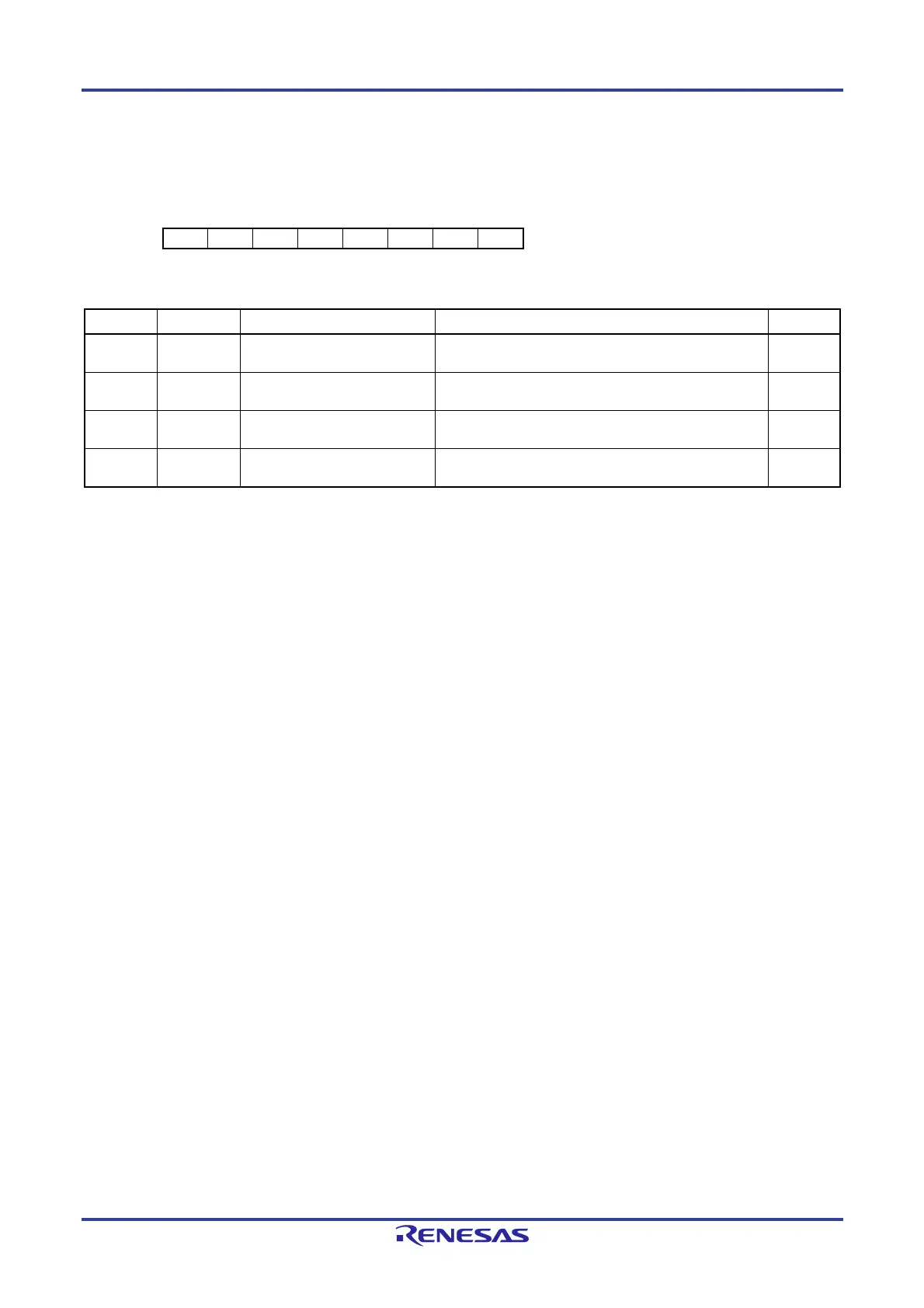

b7 b6 b5 b4 b3 b2 b1 b0

— — — — — TMOM TMTAR TMTR

After

Reset

0 0 0 0 0 0 0 0

Bit Symbol Bit Name Description R/W

7 to 3 — Reserved These bits are always read as 0. The write value should

always be 0.

R

2 TMOM One-Shot Transmission Enable 0: One-shot transmission is disabled.

1: One-shot transmission is enabled.

R/W

1 TMTAR Transmit Abort Request 0: Transmit abort is not requested.

1: Transmit abort is requested.

R/(W)

Note

0 TMTR Transmit Request 0: Transmission is not requested.

1: Transmission is requested.

R/(W)

Note

Note The only effective value for writing to this bit is 1, which sets the bit. Otherwise writing to the bit results in retention

of its state.

When the TMCp register meets any of the following conditions, set it to H'00.

• The TMCp register corresponds to the transmit buffer number selected by the CFTML[1:0] bits in the CFCCHk

register.

Bits in the TMCp register are cleared to all 0 in channel reset mode. Modify the TMCp register only in channel

communication mode or channel halt mode.

• TMOM Bit

Setting this bit to 1 enables one-shot transmission. When transmission fails, retransmission defined in the CAN

protocol is not performed.

Modify the TMOM bit when the TMTRM flag in the TMSTSp register is set to 0. To set the TMOM bit to 1, also

set the TMTR bit together.

• TMTAR Bit

Setting this bit to 1 generates a transmit abort request for the message stored in the transmit buffer. However, a

message that is being transmitted or to be transmitted next cannot be aborted.

When the TMTR bit is set to 1, the TMTAR bit can be set to 1.

The TMTAR bit is cleared to 0 when any of the following conditions is met, but is not cleared by writing 0 by the

program.

• Transmission has been completed.

• Transmit abort has been completed.

• An error or arbitration lost has been detected.

If this bit becomes 0 at the timing when the program writes 1 to this bit, this bit becomes 0.

Loading...

Loading...