RL78/F13, F14 CHAPTER 18 CAN INTERFACE (RS-CAN LITE)

R01UH0368EJ0210 Rev.2.10 1361

Dec 10, 2015

18.3.64 CANi Transmit Buffer Transmit Complete Status Register (TMTCSTS) (i = 0)

Address TMTCSTSL: F0376H, TMTCSTSH: F0377H

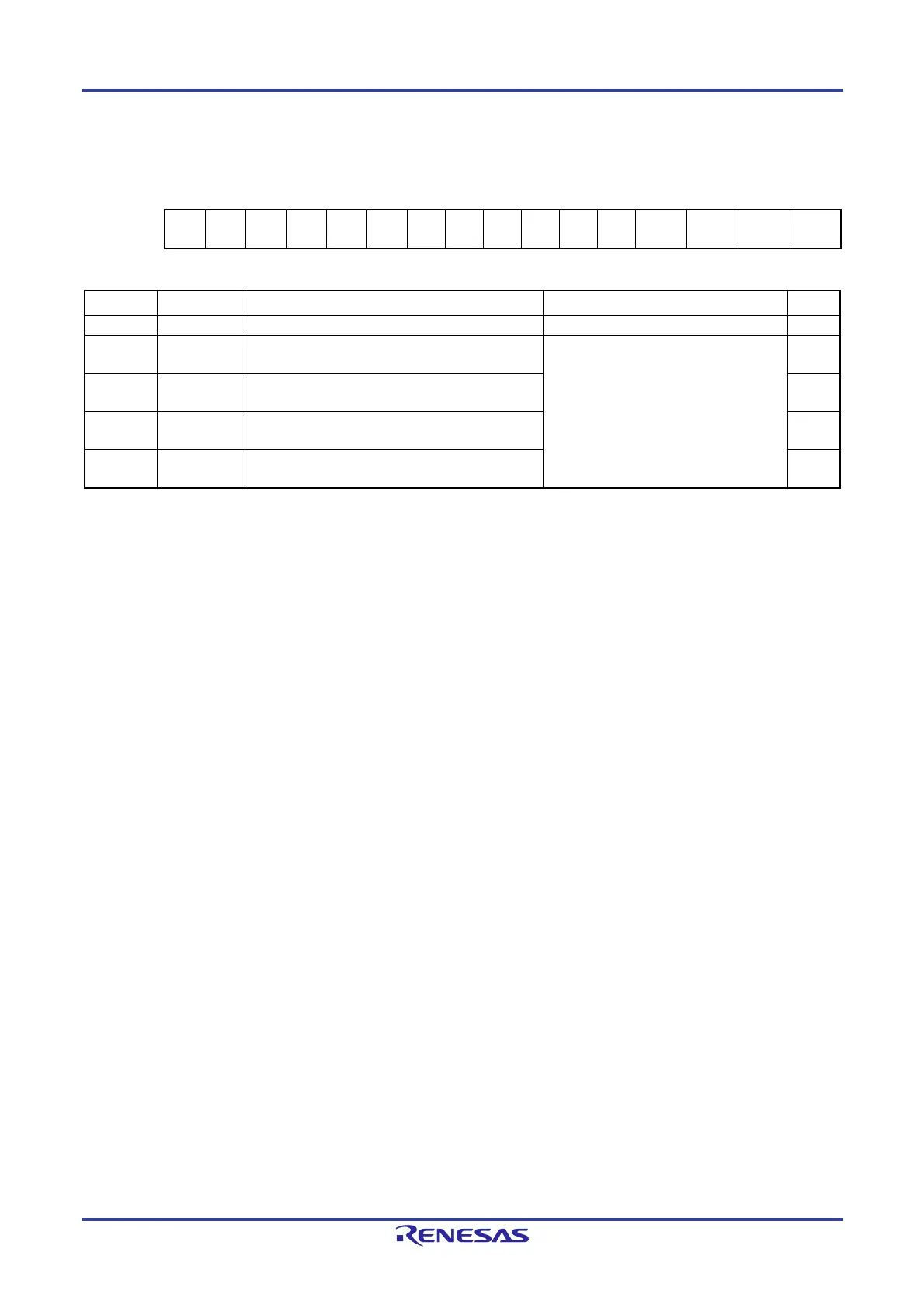

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

— — — — — — — — — — — — TMTC

STS3

TMTC

STS2

TMTC

STS1

TMTC

STS0

After Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

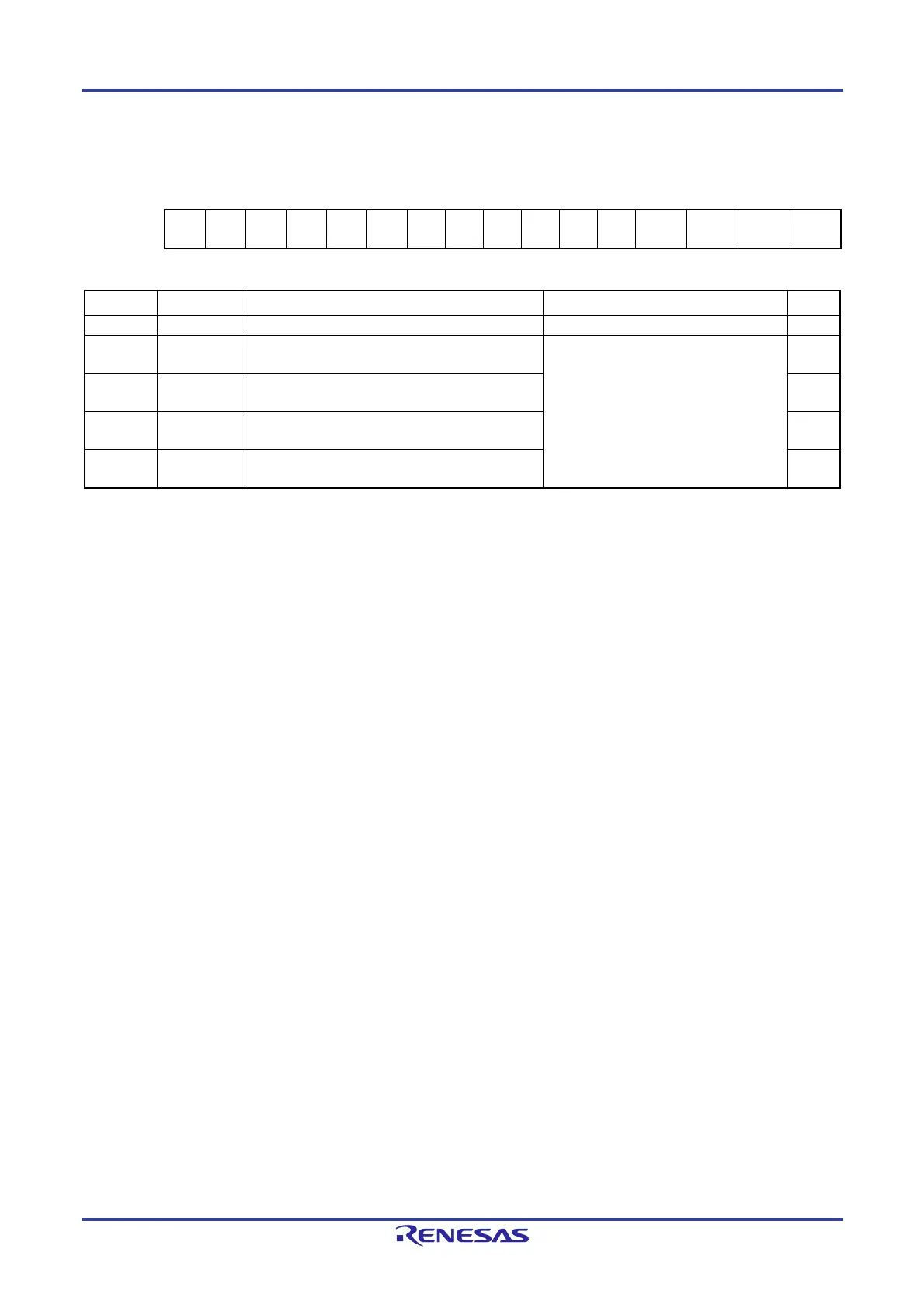

Bit Symbol Bit Name Description R/W

15 to 4 — Reserved These bits are always read as 0. R

3 TMTCSTS3 CANi Transmit Buffer 3 Transmit Complete Status

Flag

0: Transmission has not been completed.

1: Transmission has been completed

R

2 TMTCSTS2 CANi Transmit Buffer 2 Transmit Complete Status

Flag

R

1 TMTCSTS1 CANi Transmit Buffer 1 Transmit Complete Status

Flag

R

0 TMTCSTS0 CANi Transmit Buffer 0 Transmit Complete Status

Flag

R

• TMTCSTSp Flags (p = 0 to 3)

When the TMTRF[1:0] flag in the TMSTSp register is set to B'10 (transmission has been completed (without

transmit abort request)) or B'11 (transmission has been completed (with transmit abort request)), the

corresponding TMTCSTSp flag is set to 1.

These flags are cleared to 0 when the corresponding TMTRF [1:0] flag is set to B'00 or in channel reset mode.

Loading...

Loading...