RL78/F13, F14 CHAPTER 18 CAN INTERFACE (RS-CAN LITE)

R01UH0368EJ0210 Rev.2.10 1290

Dec 10, 2015

18.3.4 CANi Control Register H (CiCTRH) (i = 0)

Address C0CTRHL: F0306H, C0CTRHH: F0307H

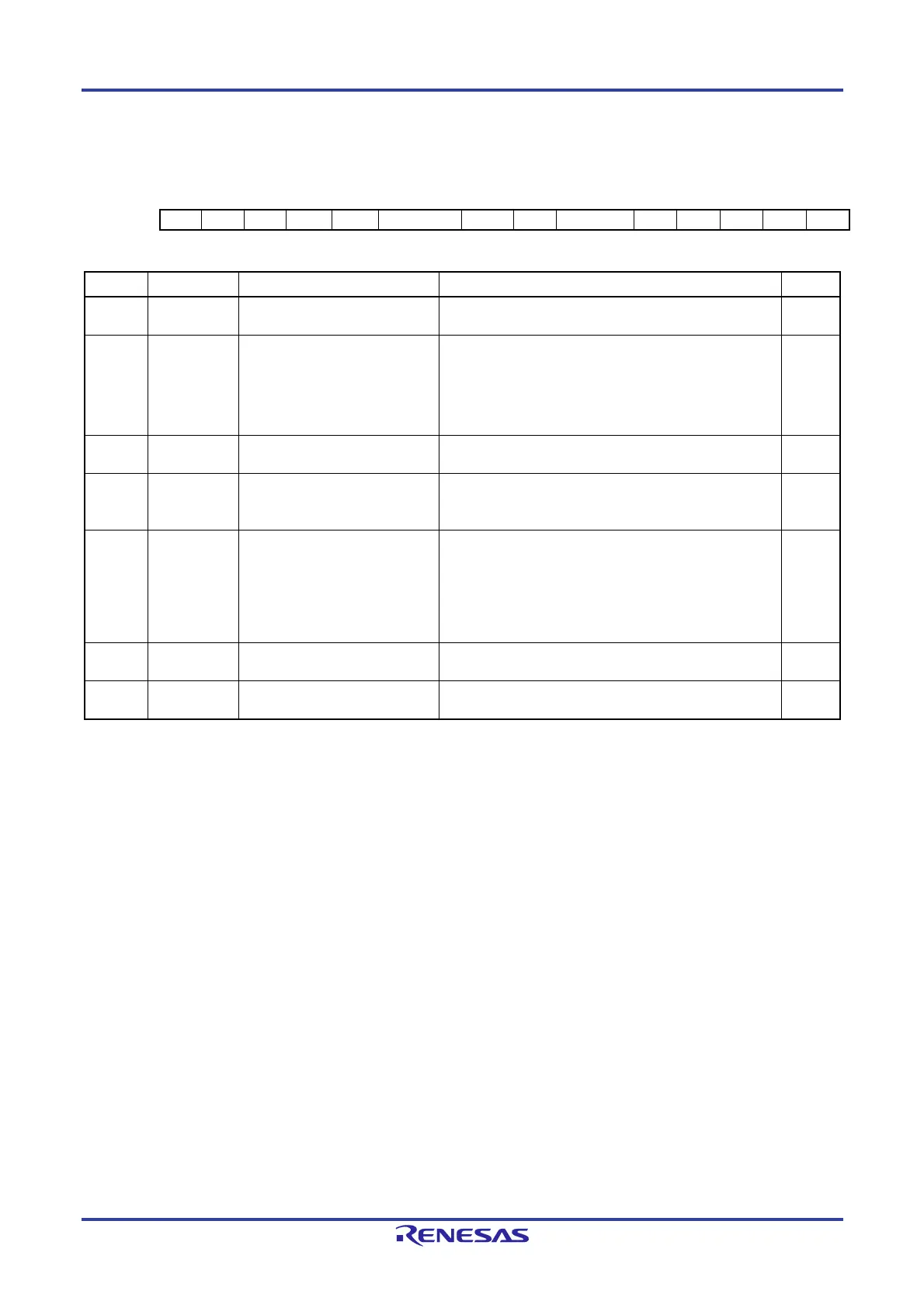

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

— — — — — CTMS[1:0] CTME ERRD BOM[1:0] — — — — TAIE

After Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

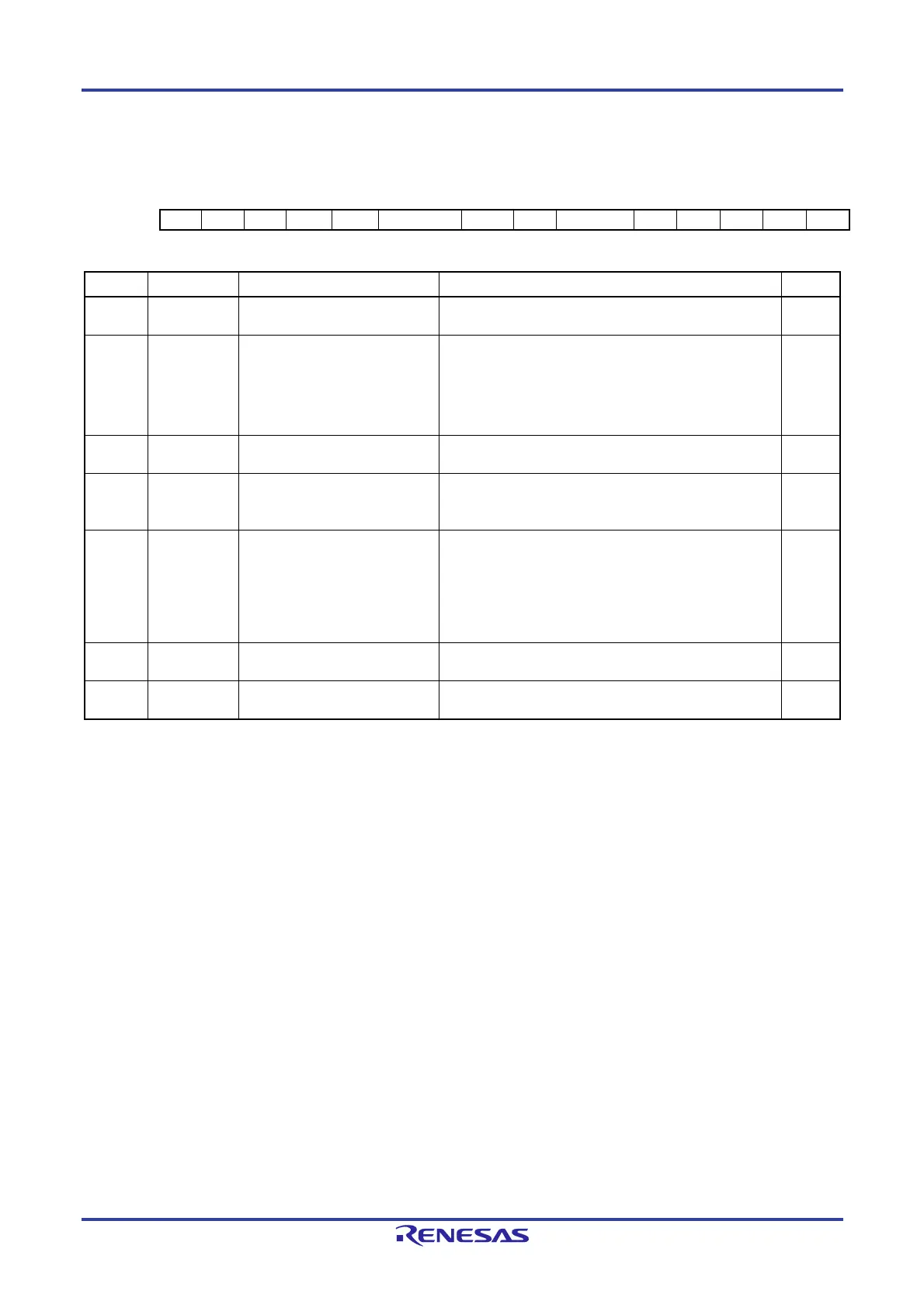

Bit Symbol Bit Name Description R/W

15 to 11 — Reserved These bits are always read as 0. The write value should

always be 0.

R

10, 9 CTMS[1:0] Communication Test Mode

Select

b10 b9

0 0: Standard test mode

0 1: Listen-only mode

1 0: Self-test mode 0 (external loopback mode)

1 1: Self-test mode 1 (internal loopback mode)

R/W

8 CTME Communication Test Mode

Enable

0: Communication test mode is disabled.

1: Communication test mode is enabled.

R/W

7 ERRD Error Display Mode Select 0: Only the first error is indicated after bits 14 to 8 in the

CiERFLL register have all been cleared.

1: The error flags of all errors are indicated.

R/W

6, 5 BOM[1:0] Bus Off Recovery Mode Select

b6 b5

0 0: ISO11898-1 compliant

0 1: Entry to channel halt mode at bus-off entry

1 0: Entry to channel halt mode at bus-off end

1 1: Entry to channel halt mode (in the bus off state) by a

program request

R/W

4 to 1 — Reserved These bits are always read as 0. The write value should

always be 0.

R

0 TAIE Transmit Abort Interrupt Enable 0: Transmit abort interrupt is disabled.

1: Transmit abort interrupt is enabled.

R/W

• CTMS[1:0] Bits

These bits are used to select a communication test mode. Modify these bits only in channel halt mode. These

bits are set to 0 in channel reset mode.

• CTME Bit

Setting this bit to 1 enables communication test mode. Modify this bit only in channel halt mode. This bit is set to

0 in channel reset mode.

• ERRD Bit

This bit is used to control display mode of bits 14 to 8 in the CiERFLL register.

When this bit is clear to 0, only the flags of the first error are set to 1. If two or more errors occur first, all the

flags of detected errors are set to 1.

When this bit is set to 1, all the flags of errors that have occurred are set to 1 regardless of the error occurrence

order. Modify this bit only in channel reset mode or channel halt mode.

Loading...

Loading...