RL78/F13, F14 CHAPTER 16 SERIAL INTERFACE IICA

R01UH0368EJ0210 Rev.2.10 1052

Dec 10, 2015

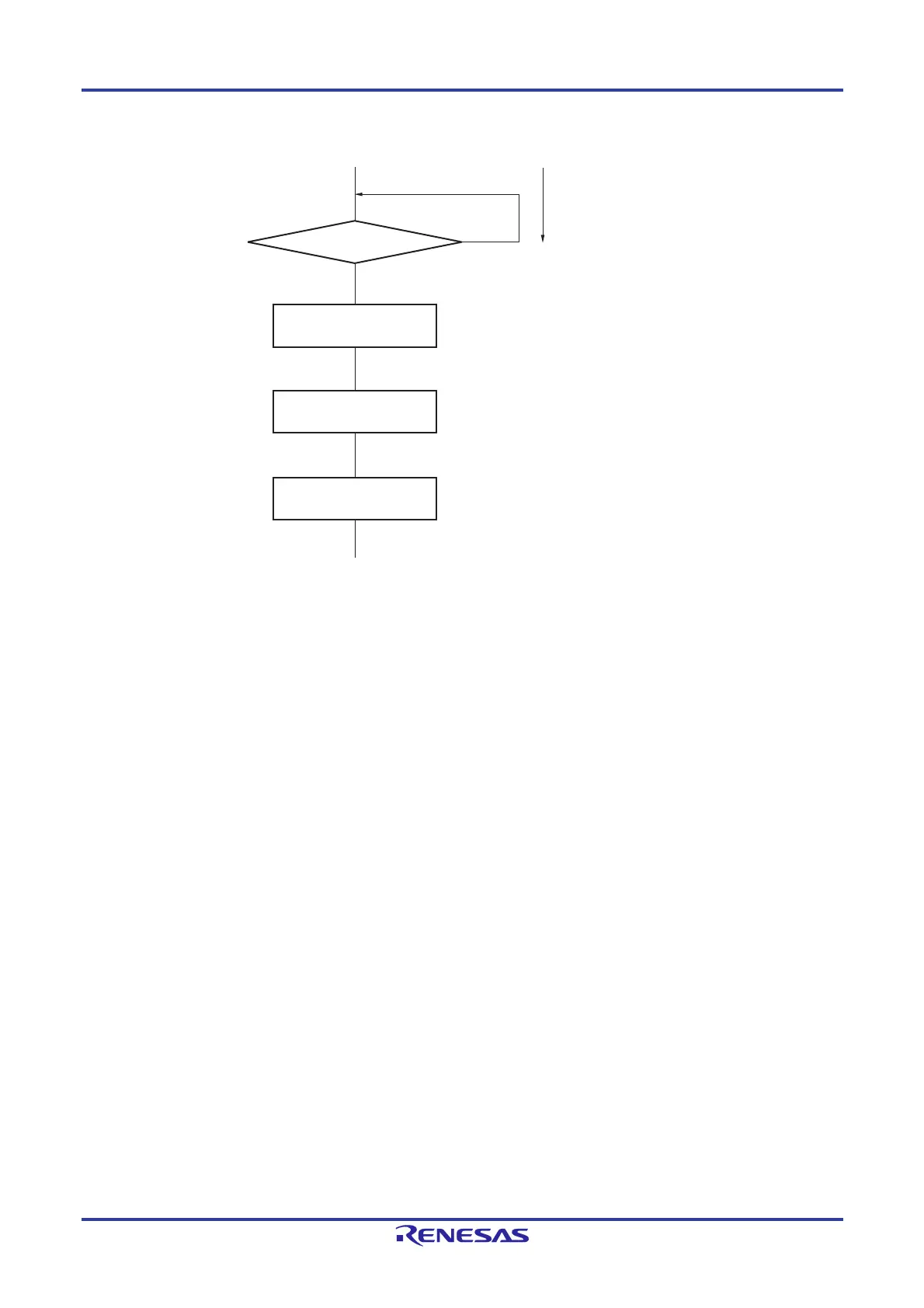

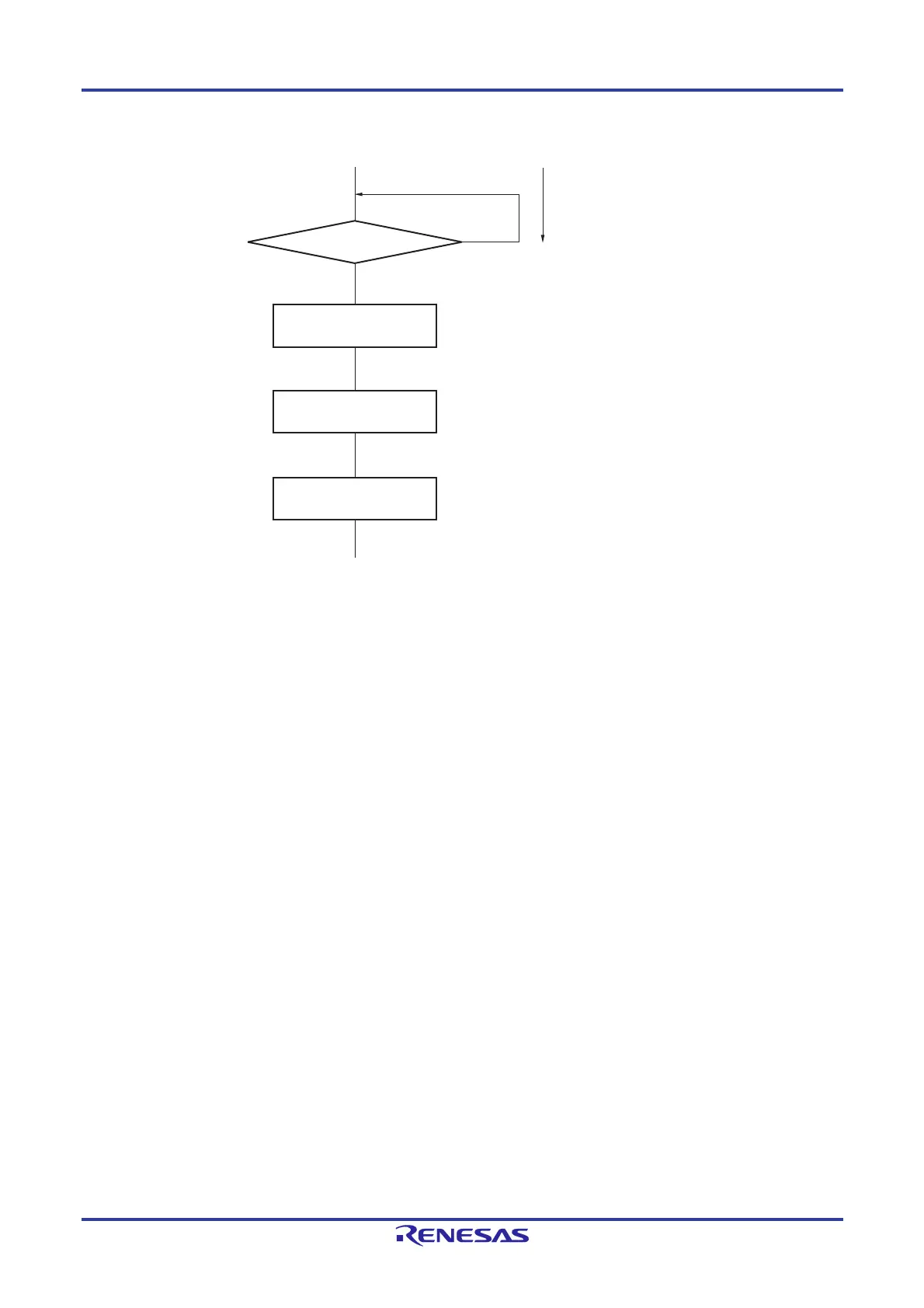

Figure 16-24. Flow When Setting WUP0 = 0 upon Address Match (Including Extension Code Reception)

Use the following flows to perform the processing to release the STOP mode other than by an interrupt request (INTIICA0)

generated from serial interface IICA.

• Master device operation: Flow shown in Figure 16-25

• Slave device operation: Same as the flow in Figure 16-24. The value of WUP0 must be kept 1 until the INTIICA0 is set

to 1.

Wait for five cycles of the operation clock (f

MCK

)

Executes processing corresponding to the operation to be executed

after checking the operation state of serial interface IICA.

STOP mode state

No

Yes

WUP0 = 0

Wait

Reading IICS0

INTIICA0 = 1?

Loading...

Loading...