RL78/F13, F14 CHAPTER 18 CAN INTERFACE (RS-CAN LITE)

R01UH0368EJ0210 Rev.2.10 1278

Dec 10, 2015

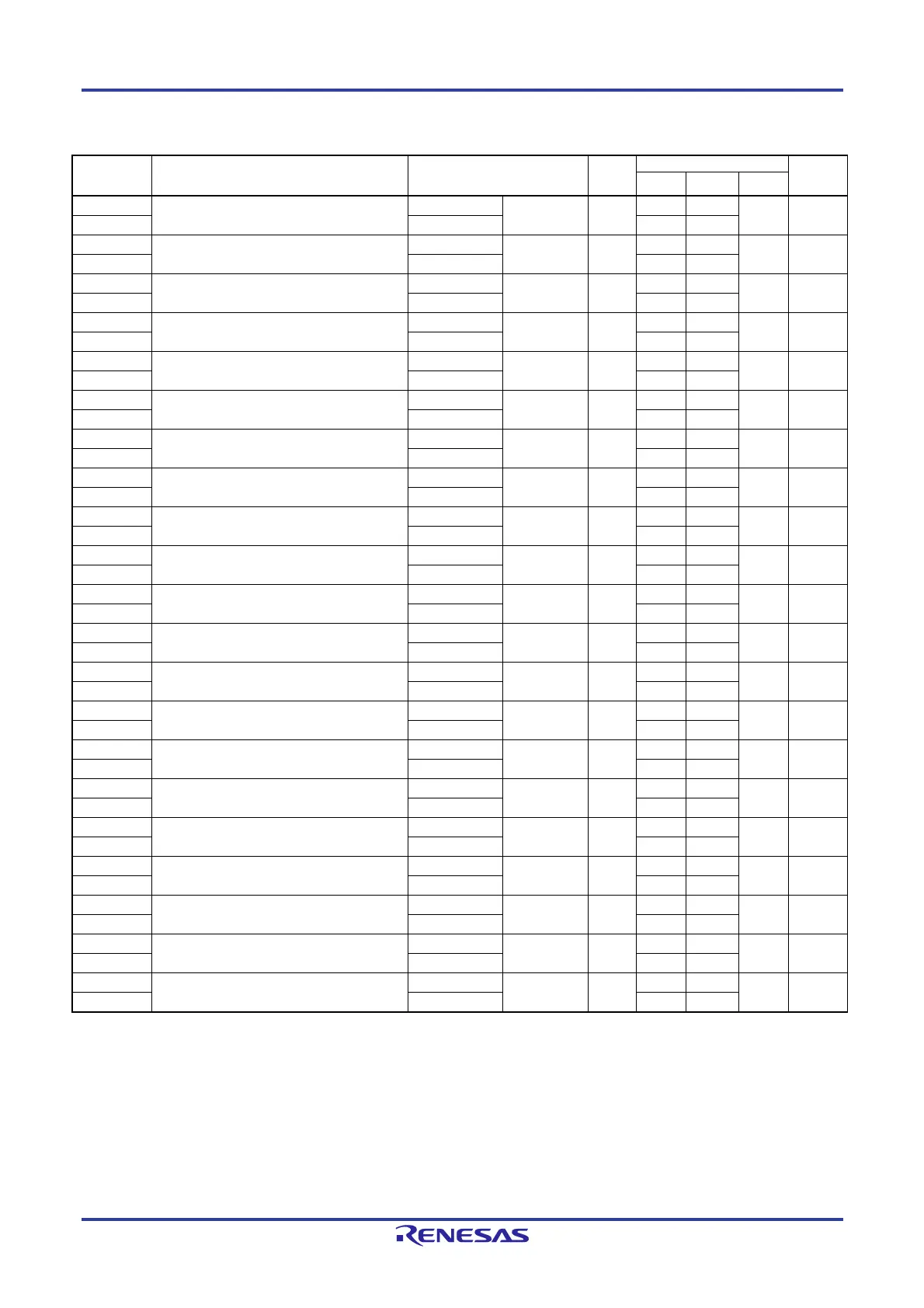

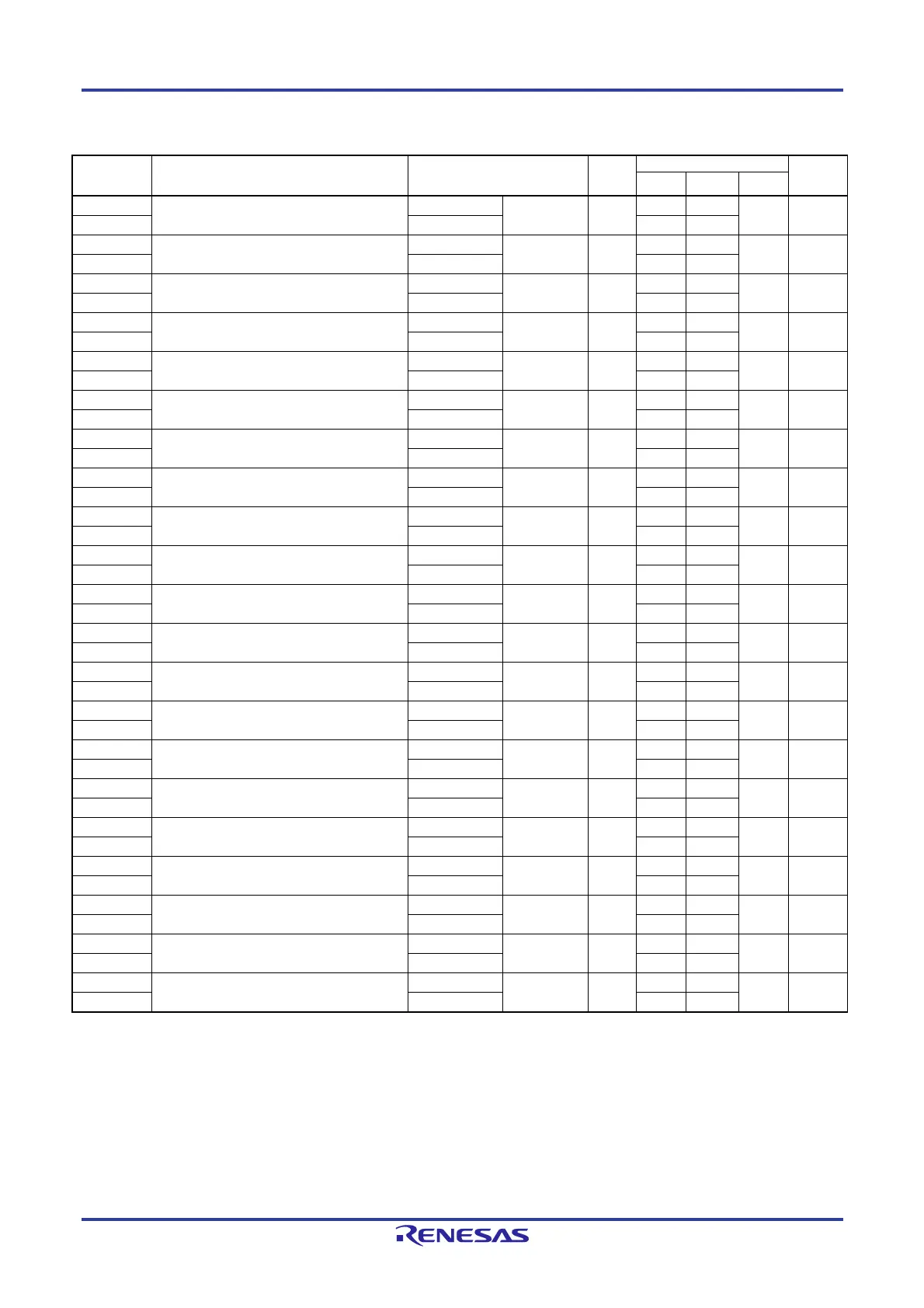

Table 18-3. List of CAN Module Registers (16/22)

Address Special Function Register (SFR) Name Symbol R/W Access Size After

Reset

1 bit 8 bits 16 bits

F05C4H CAN RAM test register 34

Note 1

RPGACC34L RPGACC34 R/W — √ √ 0000H

F05C5H RPGACC34H — √

F05C6H CAN RAM test register 35

Note 1

RPGACC35L RPGACC35 R/W — √ √ 0000H

F05C7H RPGACC35H — √

F05C8H CAN RAM test register 36

Note 1

RPGACC36L RPGACC36 R/W — √ √ 0000H

F05C9H RPGACC36H — √

F05CAH CAN RAM test register 37

Note 1

RPGACC37L RPGACC37 R/W — √ √ 0000H

F05CBH RPGACC37H — √

F05CCH CAN RAM test register 38

Note 1

RPGACC38L RPGACC38 R/W — √ √ 0000H

F05CDH RPGACC38H — √

F05CEH CAN RAM test register 39

Note 1

RPGACC39L RPGACC39 R/W — √ √ 0000H

F05CFH RPGACC39H — √

F05D0H CAN RAM test register 40

Note 1

RPGACC40L RPGACC40 R/W — √ √ 0000H

F05D1H RPGACC40H — √

F05D2H CAN RAM test register 41

Note 1

RPGACC41L RPGACC41 R/W — √ √ 0000H

F05D3H RPGACC41H — √

F05D4H CAN RAM test register 42

Note 1

RPGACC42L RPGACC42 R/W — √ √ 0000H

F05D5H RPGACC42H — √

F05D6H CAN RAM test register 43

Note 1

RPGACC43L RPGACC43 R/W — √ √ 0000H

F05D7H RPGACC43H — √

F05D8H CAN RAM test register 44

Note 1

RPGACC44L RPGACC44 R/W — √ √ 0000H

F05D9H RPGACC44H — √

F05DAH CAN RAM test register 45

Note 1

RPGACC45L RPGACC45 R/W — √ √ 0000H

F05DBH RPGACC45H — √

F05DCH CAN RAM test register 46

Note 1

RPGACC46L RPGACC46 R/W — √ √ 0000H

F05DDH RPGACC46H — √

F05DEH CAN RAM test register 47

Note 1

RPGACC47L RPGACC47 R/W — √ √ 0000H

F05DFH RPGACC47H — √

F05E0H CAN RAM test register 48

Note 1

RPGACC48L RPGACC48 R/W — √ √ 0000H

F05E1H RPGACC48H — √

F05E0H CAN0 transmit/receive FIFO access

register 0AL

Note 2

CFIDL0L CFIDL0 R/W — √ √ 0000H

F05E1H CFIDL0H — √

F05E2H CAN RAM test register 49

Note 1

RPGACC49L RPGACC49 R/W — √ √ 0000H

F05E3H RPGACC49H — √

F05E2H CAN0 transmit/receive FIFO access

register 0AH

Note 2

CFIDH0L CFIDH0 R/W — √ √ 0000H

F05E3H CFIDH0H — √

F05E4H CAN RAM test register 50

Note 1

RPGACC50L RPGACC50 R/W — √ √ 0000H

F05E5H RPGACC50H — √

F05E4H CAN0 transmit/receive FIFO access

register 0BL

Note 2

CFTS0L CFTS0 R — √ √ 0000H

F05E5H CFTS0H — √

F05E6H CAN RAM test register 51

Note 1

RPGACC51L RPGACC51 R/W — √ √ 0000H

F05E7H RPGACC51H — √

Notes 1. These registers are allocated to RAM window 0 for the CAN module (receive rules and CAN RAM test

register). When setting these registers, set the RPAGE bit in the GRWCR register to 0.

2. These registers are allocated to RAM window 1 for the CAN module (receive buffer, receive FIFO buffer,

transmit/receive FIFO buffer, transmit buffer, and transmit history data). When setting these registers, set the

RPAGE bit in the GRWCR register to 1.

Loading...

Loading...