RL78/F13, F14 CHAPTER 24 RESET FUNCTION

R01UH0368EJ0210 Rev.2.10 1545

Dec 10, 2015

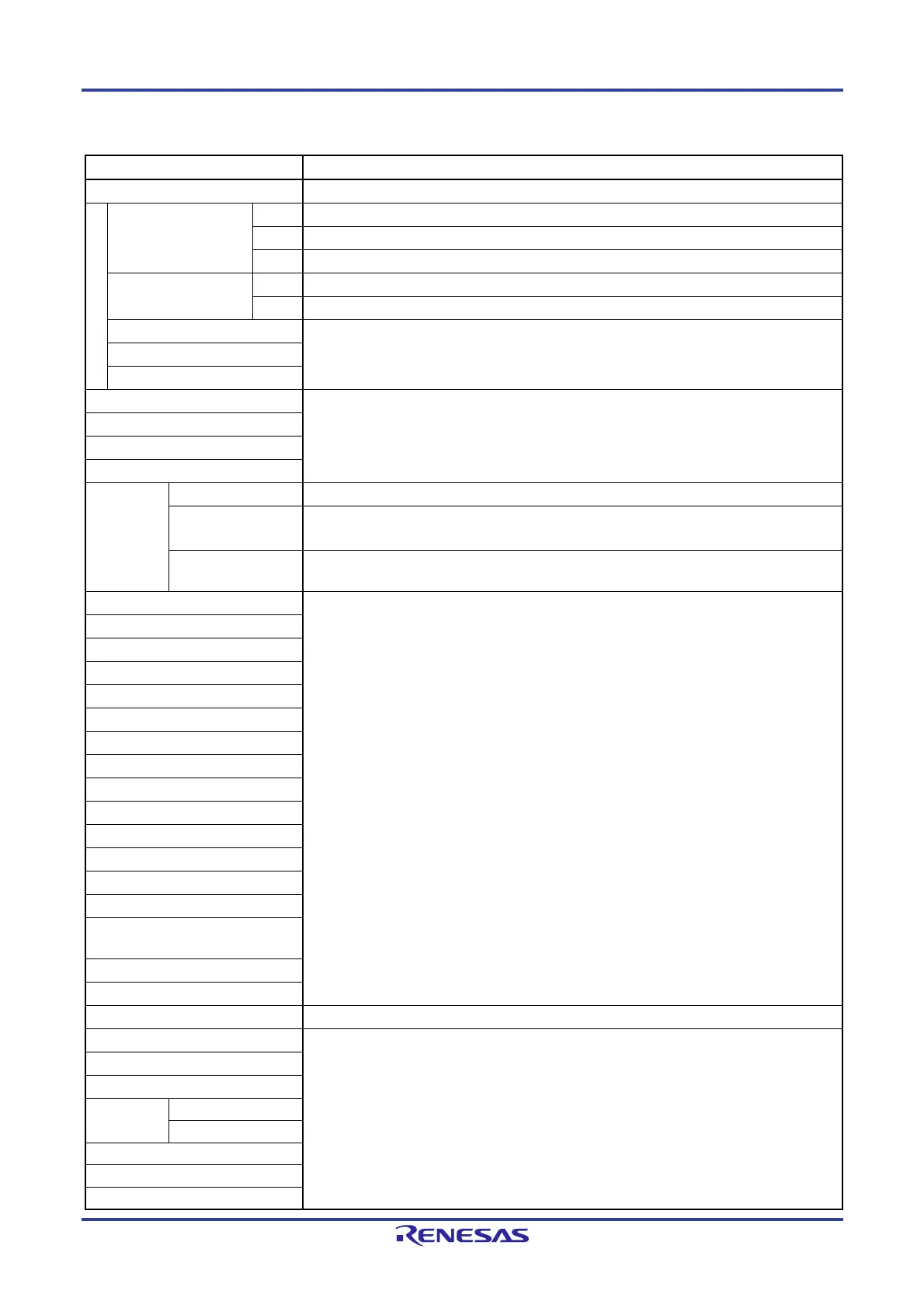

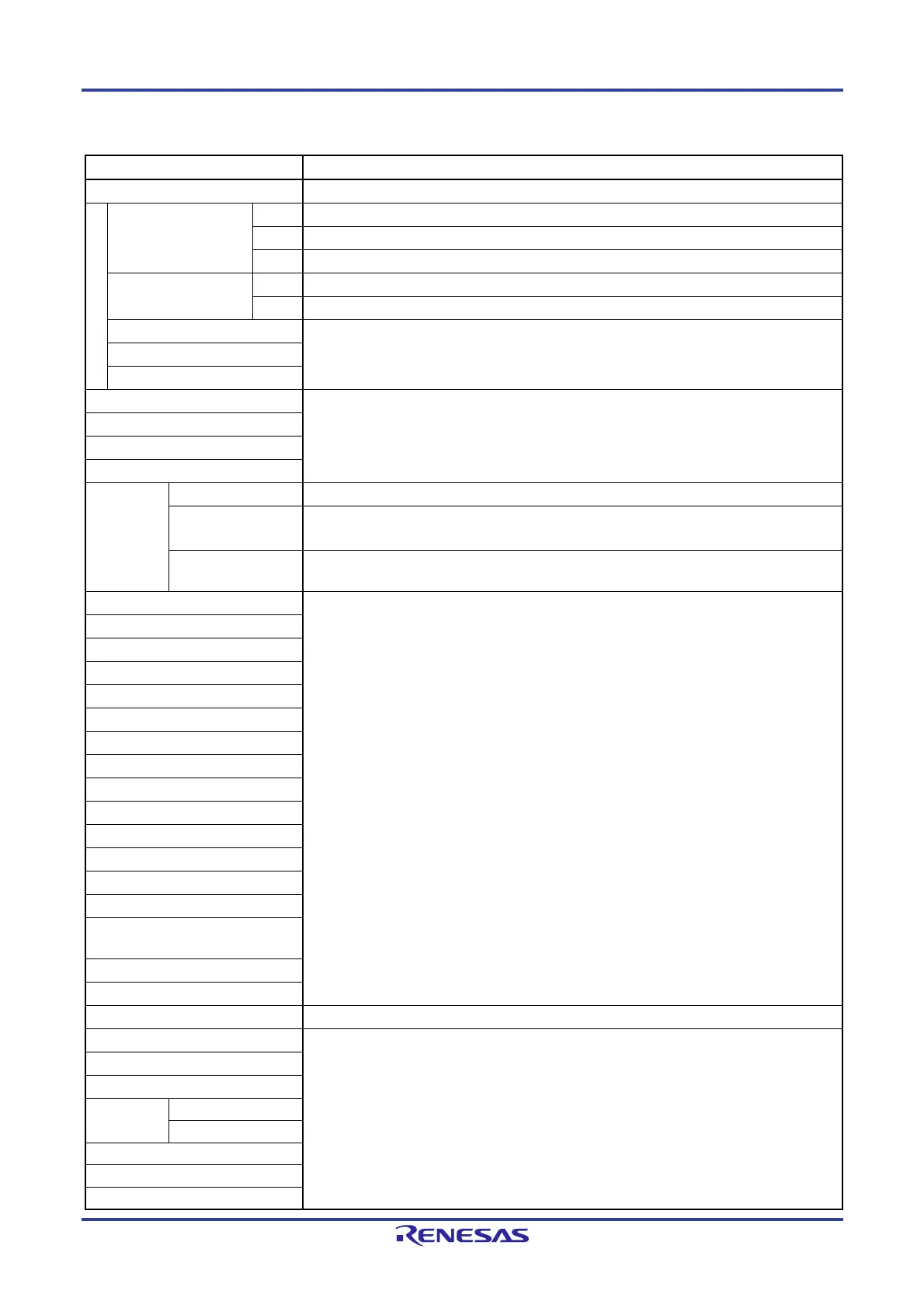

Table 24-1. Operation Statuses During Reset Period

Item During Reset Period

System clock Clock supply to the CPU is stopped.

Main system clock fIH Operation stopped

fX Operation stopped (the X1 and X2 pins are input port mode)

fEX Clock input invalid (the pin is input port mode)

Subsystem clock fXT Operation stopped (the XT1 and XT2 pins are input port mode)

fEXS Clock input invalid (the pin is input port mode)

fIL Operation stopped

fPLL

fWDT

CPU Operation stopped

Code flash memory

Data flash memory

RAM

Port (latch) P130 Outputs the low level

P40 High impedance (by an external reset or POR reset)

Pulled up (by reset other than external reset or POR reset)

Other than P130 and

P40

High impedance

Timer array unit Operation stopped

Timer RJ

Timer RD

Real-time clock (RTC)

Watchdog timer

Clock monitor

Clock output/buzzer output

A/D converter

D/A converter

Note

Comparator

Note

Serial array unit (SAU)

Serial interface (IICA)

LIN/UART module (RLIN3)

CAN interface (RS-CAN lite)

Multiplier and Divider/Multiply-

Accumulator

DTC

ELC

Note

Power-on-reset function Detection operation possible

Low-voltage detection function Operation stopped

External interrupt

Key interrupt function

CRC operation

function

High-speed CRC

General-purpose CRC

Illegal-memory access detection function

RAM guard function

SFR guard function

Loading...

Loading...