RL78/F13, F14 CHAPTER 8 TIMER RD

R01UH0368EJ0210 Rev.2.10 610

Dec 10, 2015

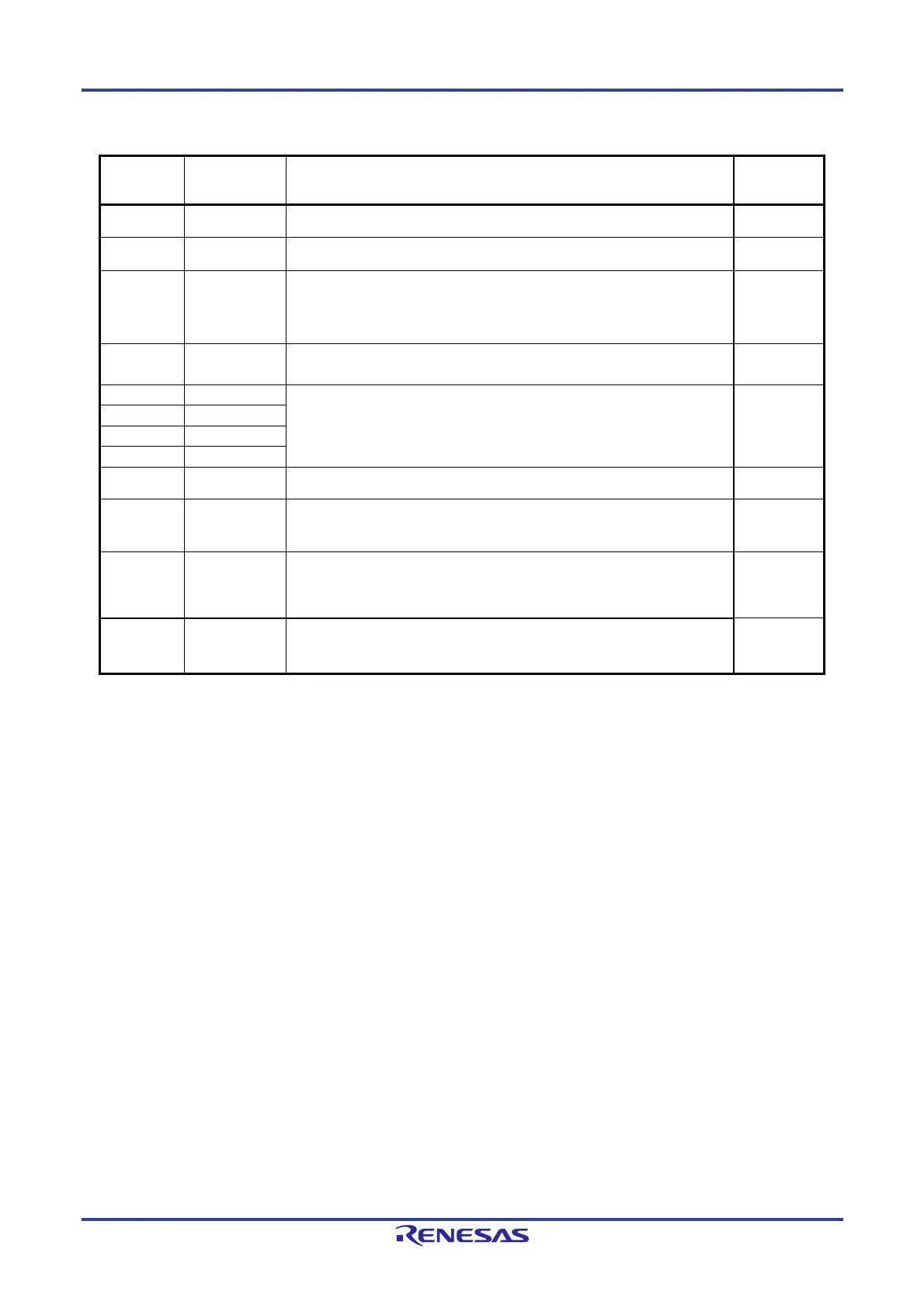

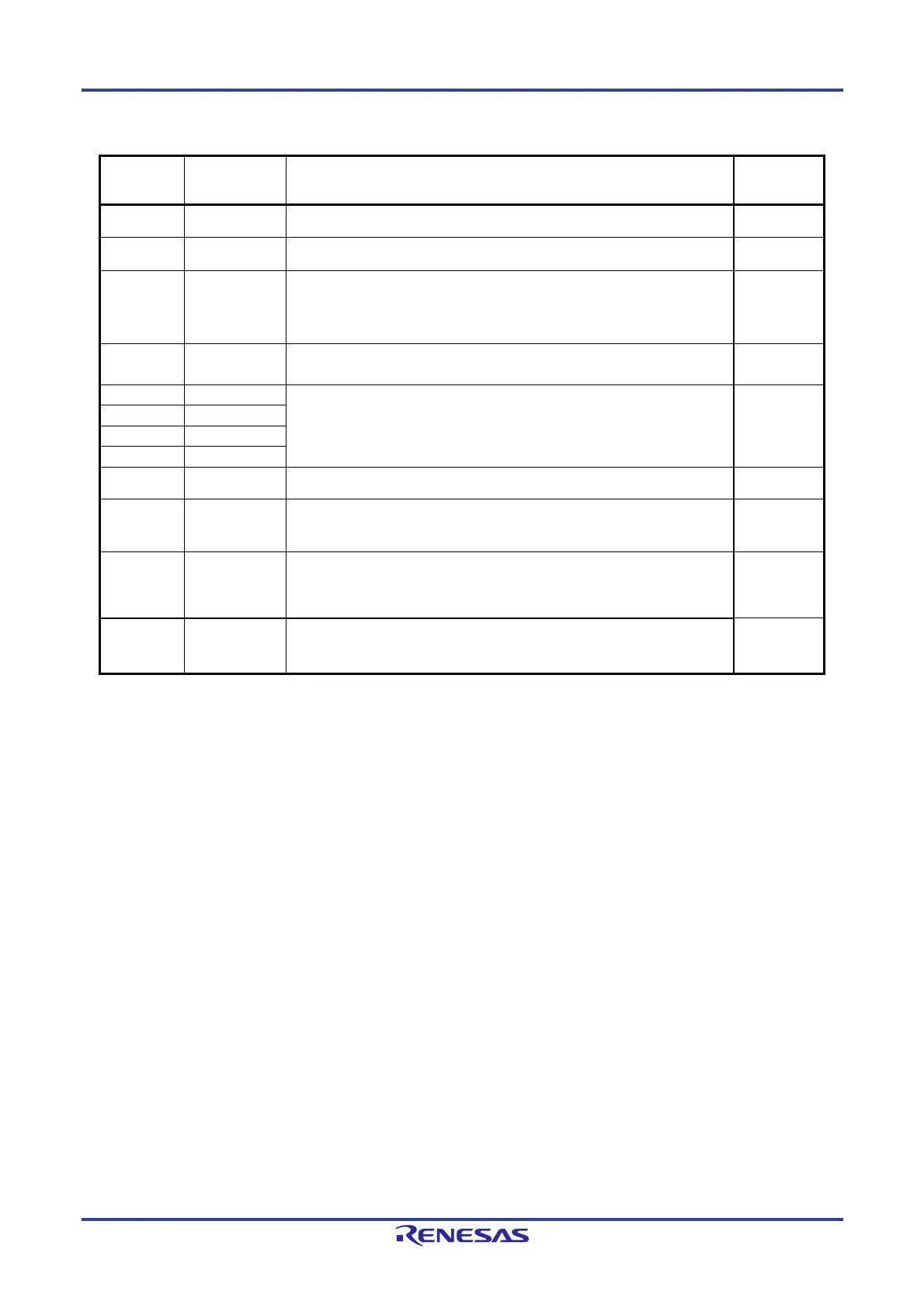

Table 8-8. TRDGRji Register Functions in PWM3 Mode

Register Setting Register Function PWM Output

Pin

TRDGRA0 — General register. Set the PWM period .

Setting range: Value set in TRDGRA1 register

TRDIOA0

TRDGRA1

—

General register. Set the changing point (active level timing) of PWM output

Setting range: Value set in TRDGRA0 register

—

TRDGRB0

— General register. Set the changing point (the timing for returning to initial

output level) of PWM output.

Setting range: Value set in TRDGRB1 register and Value set in

TRDGRA0 register

TRDIOB0

TRDGRB1 — General register. Set the changing point (active level timing) of PWM output

Setting range: Value set in TRDGRB0 register

—

TRDGRC0 TRDBFC0 = 0 (Not used in PWM3 mode.) —

TRDGRC1 TRDBFC1 = 0

TRDGRD0 TRDBFD0 = 0

TRDGRD1 TRDBFD1 = 0

TRDGRC0 TRDBFC0 = 1 Buffer register. Set the next PWM period (see 8. 3. 1 (2) Buffer Operation).

Setting range: Value set in TRDGRC1 register

TRDIOA0

TRDGRC1 TRDBFC1 = 1 Buffer register. Set the changing point of next PWM output

(see 8. 3. 1 (2) Buffer Operation).

Setting range: Value set in TRDGRC0 register

—

TRDGRD0 TRDBFD0 = 1 Buffer register. Set the changing point of next PWM output

(see 8. 3. 1 (2) Buffer Operation).

Setting range: Value set in TRDGRD1 register and Value set in

TRDGRC0 register

TRDIOB0

TRDGRD1 TRDBFD1 = 1 Buffer register. Set the changing point of next PWM output

(see 8. 3. 1 (2) Buffer Operation).

Setting range: Value set in TRDGRD0 register

—

Caution When the setting of bits TCK2 to TCK0 in the TRDCR0 register is 000B (fCLK, fIH, fPLL, fSUB, and fIL) and

the compare value is set to 0000H, a request signal to the data transfer controller (DTC) and the event

link controller (ELC) is generated only once immediately after the count starts. When the compare

value is 0001H or higher, a request signal is generated each time a compare match occurs.

Remark i = 0 or 1, j = A, B, C, or D

TRDBFC0, TRDBFD0, TRDBFC1, TRDBFD1: Bits in TRDMR register

Loading...

Loading...