RL78/F13, F14 CHAPTER 8 TIMER RD

R01UH0368EJ0210 Rev.2.10 614

Dec 10, 2015

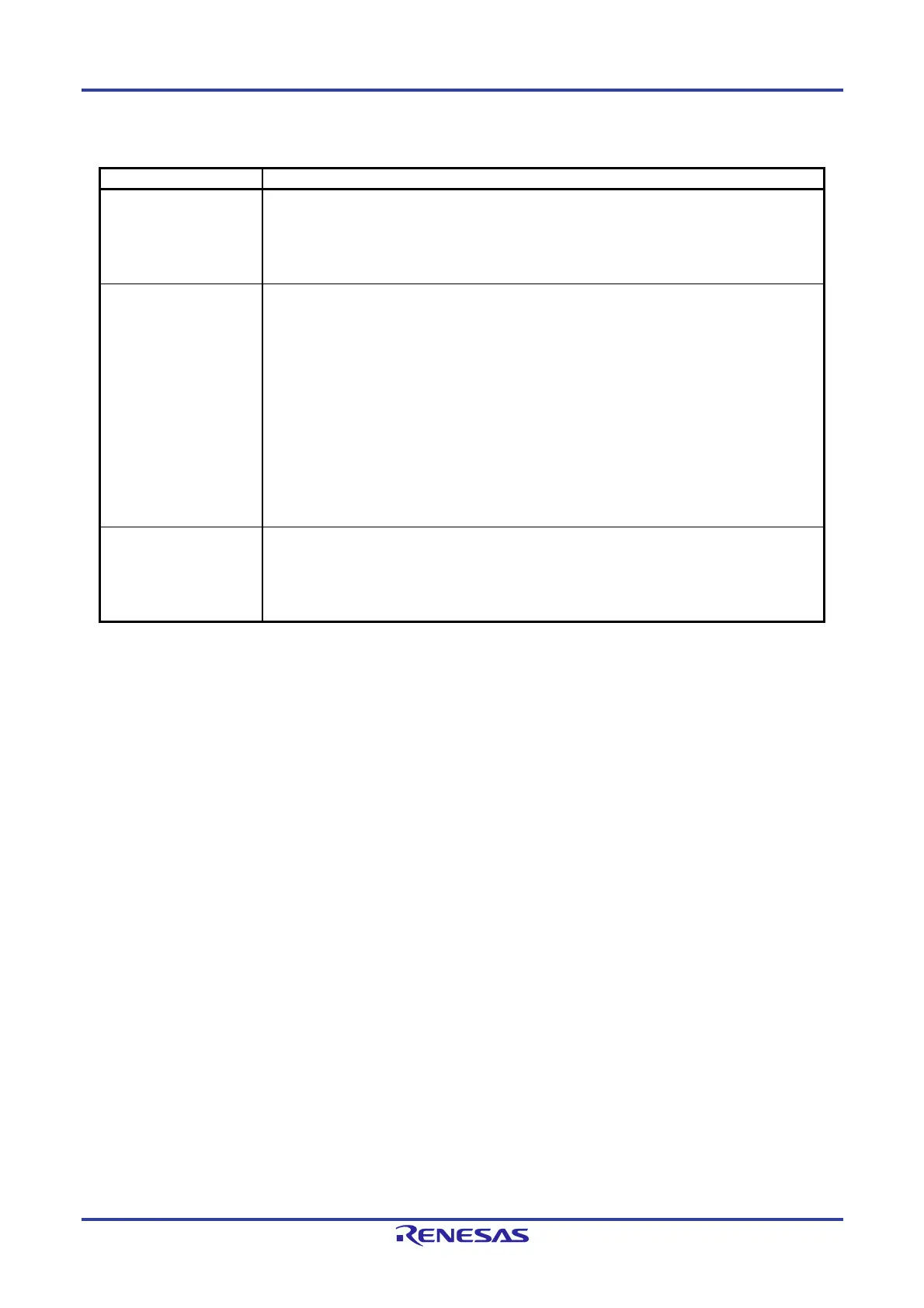

Notes on count source setting is described below.

Notes on Count Source Setting of Timer RD

Count Source Notes on Setting

fCLK, fCLK/2, fCLK/4, fCLK/8,

f

CLK/32

Set the TRD_CKSEL bit in the CKSEL register to 0 (f

CLK/fMP is selected), the FRQSEL4 bit in the

user option byte (000C2H/020C2H) to 0 (f

IH32 MHz), and the PLLDIV1 bit in the PLLCTL register

to 0 (f

PLL32 MHz).

Do not set f

CLK/2, fCLK/4, fCLK/8, or fCLK/32 when FRQSEL4 = 1.

The count sources cannot be used when SNOOZE status is output.

fIH, fPLL When fIH/fPLL (64 MHz or 48 MHz) or fPLL (over 32 MHz) is used, set the CSS bit in the CKC register

to 0 (f

CLK = fMP is selected).

When f

IH/fPLL (64 MHz or 48 MHz) is used, set bits MDIV2 to MDIV0 in the MDIV register to 001B

(f

MP/2 is selected)

When f

IH/fPLL (64 MHz or 48 MHz) or fPLL (over 32 MHz) is used, set the TRD_CKSEL bit in the

CKSEL register to 0 (f

CLK/fMP is selected).

When f

IH/fPLL (64 MHz or 48 MHz) or fPLL (over 32 MHz) is used, set the CSS bit, MDIV2 to MDIV0

bits, and TRD_CKSEL bit before setting the TRD0EN bit in the PER1 register.

Set the f

CLK to the clock source which is same as the count source before setting bit 4 (TRD0EN) in

the peripheral enable register 1 (PER1).

Setting the FRQSEL4 bit in the user option byte (000C2H/020C2H) to 1 (f

IH = 64 MHz/48 MHz) and

the PLLDIV bit in the PLLCTL register to 1 (f

PLL > 32 MHz) is prohibited.

The count sources cannot be used when SNOOZE status is output.

fSUB, fIL When the CPU accesses the timer RD register, set the CSS bit in the CKC register to 1 (fCLK = fSL is

selected).

Set the f

CLK to the clock source which is same as the count source before setting bit 4 (TRD0EN) in

the peripheral enable register 1 (PER1).

The count sources should be set when SNOOZE status is output.

Loading...

Loading...