ADC Operation

www.ti.com

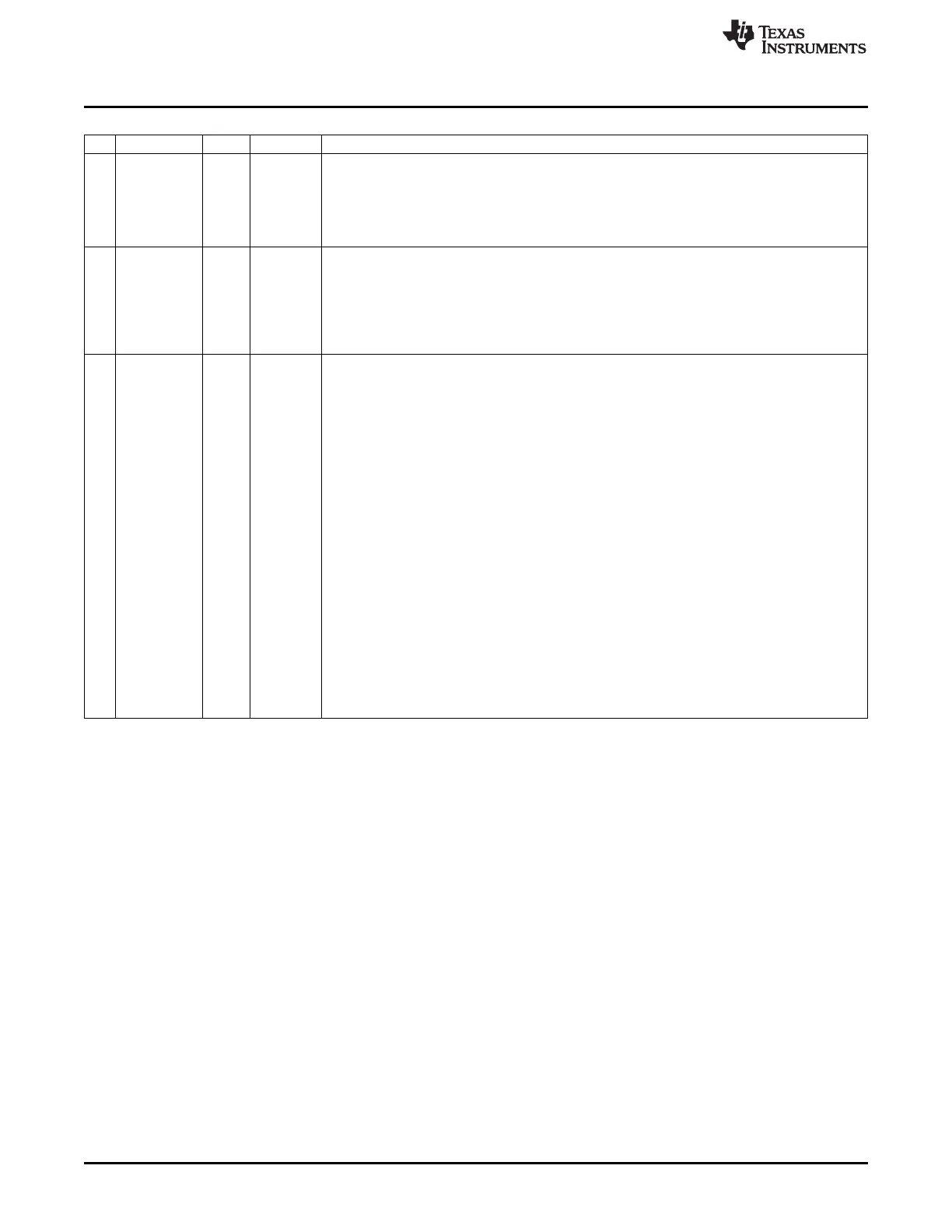

ADCCON2 (0xB5) – ADC Control 2

Bit Name Reset R/W Description

7:6

SREF[1:0]

00 R/W Selects reference voltage used for the sequence of conversions

00: Internal reference

01: External reference on AIN7 pin

10: AVDD5 pin

11: External reference on AIN6–AIN7 differential input

5:4

SDIV[1:0]

01 R/W Sets the decimation rate for channels included in the sequence of conversions. The decimation

rate also determines the resolution and time required to complete a conversion.

00: 64 decimation rate (7 bits ENOB setting)

01: 128 decimation rate (9 bits ENOB setting)

10: 256 decimation rate (10 bits ENOB setting)

11: 512 decimation rate (12 bits ENOB setting)

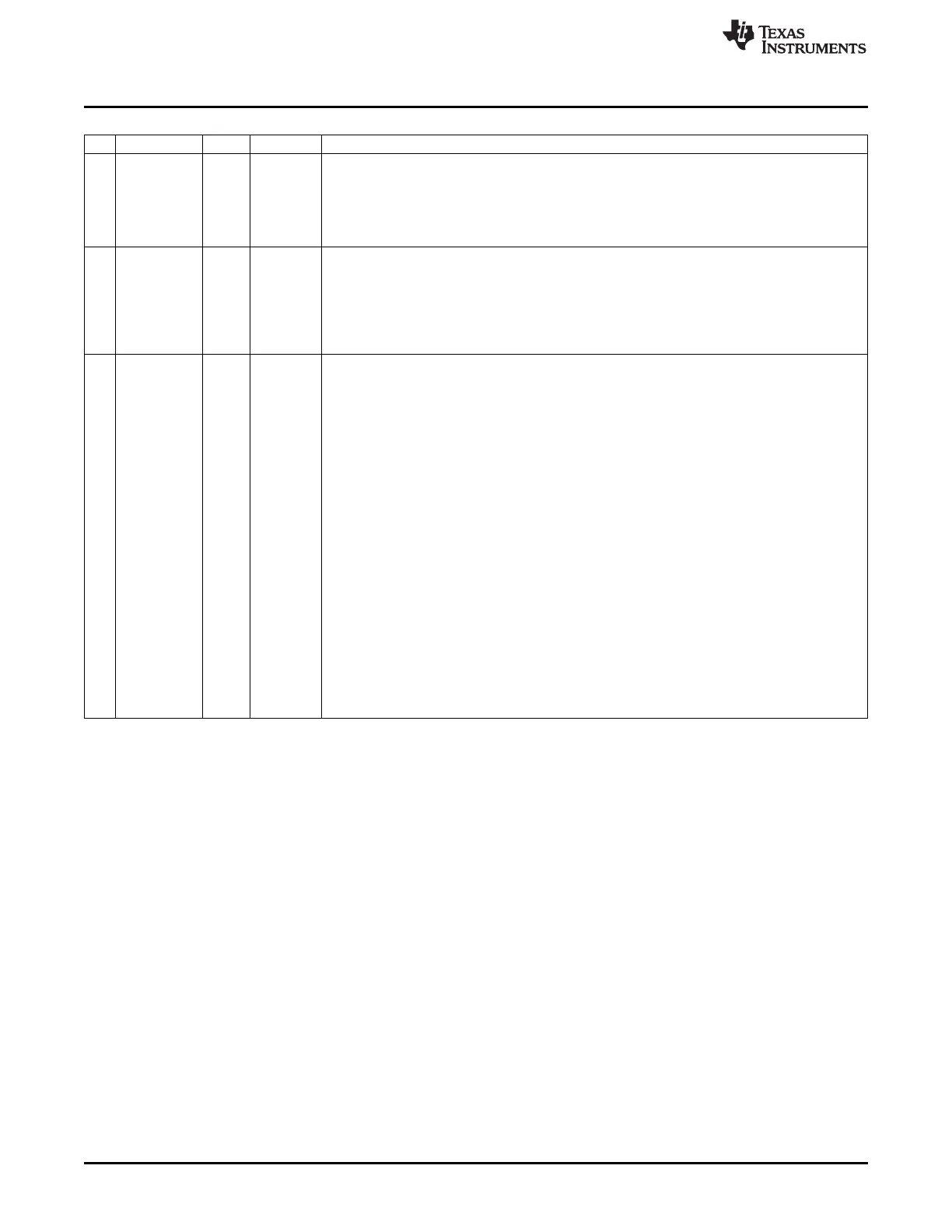

3:0

SCH[3:0]

0000 R/W Sequence channel select. Selects the end of the sequence. A sequence can either be from AIN0

to AIN7 (SCH ≤ 7) or from differential input AIN0–AIN1 to AIN6–AIN7 (8 ≤ SCH ≤ 11). For other

settings, only one conversions is performed.

When read, these bits indicate the channel number on which a conversion is ongoing.

0000: AIN0

0001: AIN1

0010: AIN2

0011: AIN3

0100: AIN4

0101: AIN5

0110: AIN6

0111: AIN7

1000: AIN0–AIN1

1001: AIN2–AIN3

1010: AIN4–AIN5

1011: AIN6–AIN7

1100: GND

1101: Reserved

1110: Temperature sensor

1111: VDD/3

142

ADC SWRU191C–April 2009–Revised January 2012

Submit Documentation Feedback

Copyright © 2009–2012, Texas Instruments Incorporated

Loading...

Loading...