USART Registers

www.ti.com

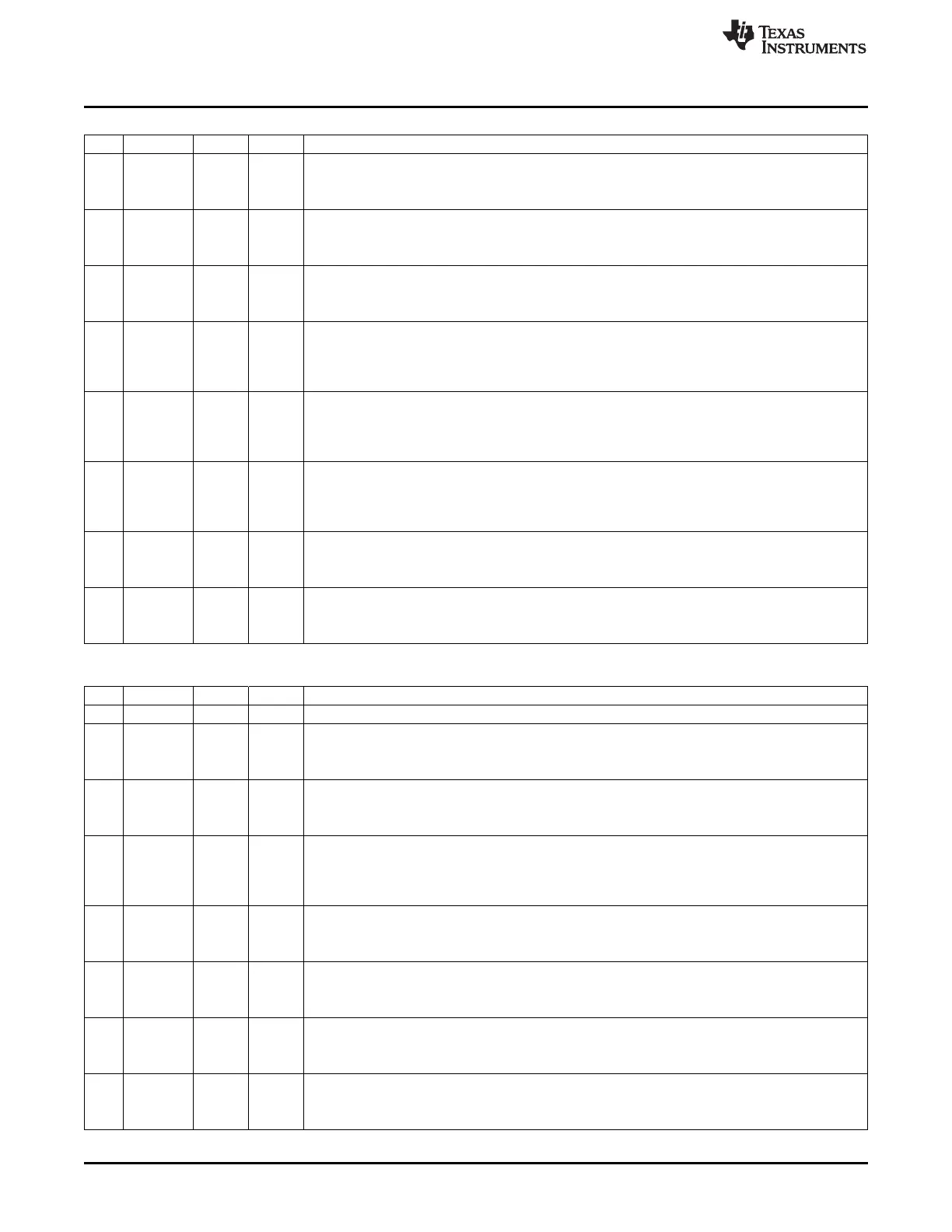

U1CSR (0xF8) – USART 1 Control and Status

Bit Name Reset R/W Description

7

MODE

0 R/W USART mode select

0: SPI mode

1: UART mode

6

RE

0 R/W UART receiver enable. Note: Do not enable receive before UART is fully configured.

0: Receiver disabled

1: Receiver enabled

5

SLAVE

0 R/W SPI master- or slave-mode select

0: SPI master

1: SPI slave

4

FE

0 R/W0

UART framing error status. This bit is automatically cleared on a read of the U1CSR register or bits

in the U1CSR register.

0: No framing error detected

1: Byte received with incorrect stop-bit level

3

ERR

0 R/W0

UART parity error status. This bit is automatically cleared on a read of the U1CSR register or bits in

the U1CSR register.

0: No parity error detected

1: Byte received with parity error

2

RX_BYTE

0 R/W0 Receive byte status. UART mode and SPI slave mode. This bit is automatically cleared when

reading U1DBUF; clearing this bit by writing 0 to it effectively discards the data in U1DBUF.

0: No byte received

1: Received byte ready

1

TX_BYTE

0 R/W0 Transmit byte status. UART mode and SPI master mode

0: Byte not transmitted

1: Last byte written to data buffer register has been transmitted

0

ACTIVE

0 R USART transmit/receive active status. In SPI slave mode, this bit equals slave select.

0: USART idle

1: USART busy in transmit or receive mode

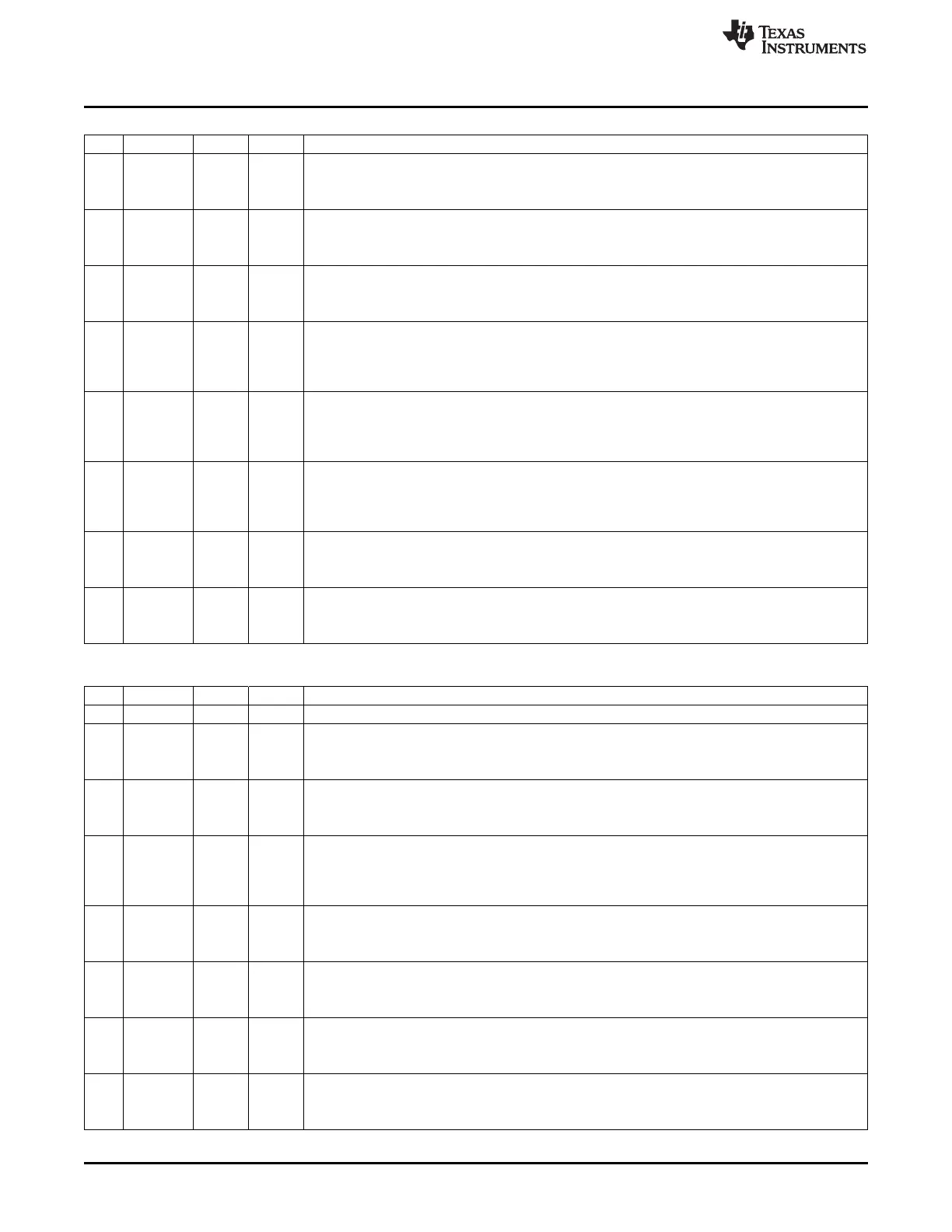

U1UCR (0xFB) – USART 1 UART Control

Bit Name Reset R/W Description

7

FLUSH

0 R0/W1 Flush unit. When set, this event stops the current operation and returns the unit to the idle state.

6

FLOW

0 R/W UART hardware flow enable. Selects use of hardware flow control with RTS and CTS pins

0: Flow control disabled

1: Flow control enabled

5

D9

0 R/W

If parity is enabled (see PARITY, bit 3 in this register), then this bit sets the parity level as follows.

0: Odd parity

1: Even parity

4

BIT9

0 R/W Set this bit to 1 in order to enable the parity bit tranfer (as 9th bit). The content of this 9th bit is given

by D9, if parity is enabled by PARITY.

0: 8-bit transfer

1: 9-bit transfer

3

PARITY

0 R/W

UART parity enable. One must set BIT9 in addition to setting this bit for parity to be calculated.

0: Parity disabled

1: Parity enabled

2

SPB

0 R/W UART number of stop bits. Selects the number of stop bits to transmit

0: 1 stop bit

1: 2 stop bits

1

STOP

1 R/W UART stop-bit level must be different from start-bit level.

0: Low stop bit

1: High stop bit

0

START

0 R/W UART start-bit level. Ensure that the polarity of the start bit is opposite the level of the idle line.

0: Low start bit

1: High start bit

170

USART SWRU191C–April 2009–Revised January 2012

Submit Documentation Feedback

Copyright © 2009–2012, Texas Instruments Incorporated

Loading...

Loading...