www.ti.com

Interrupts

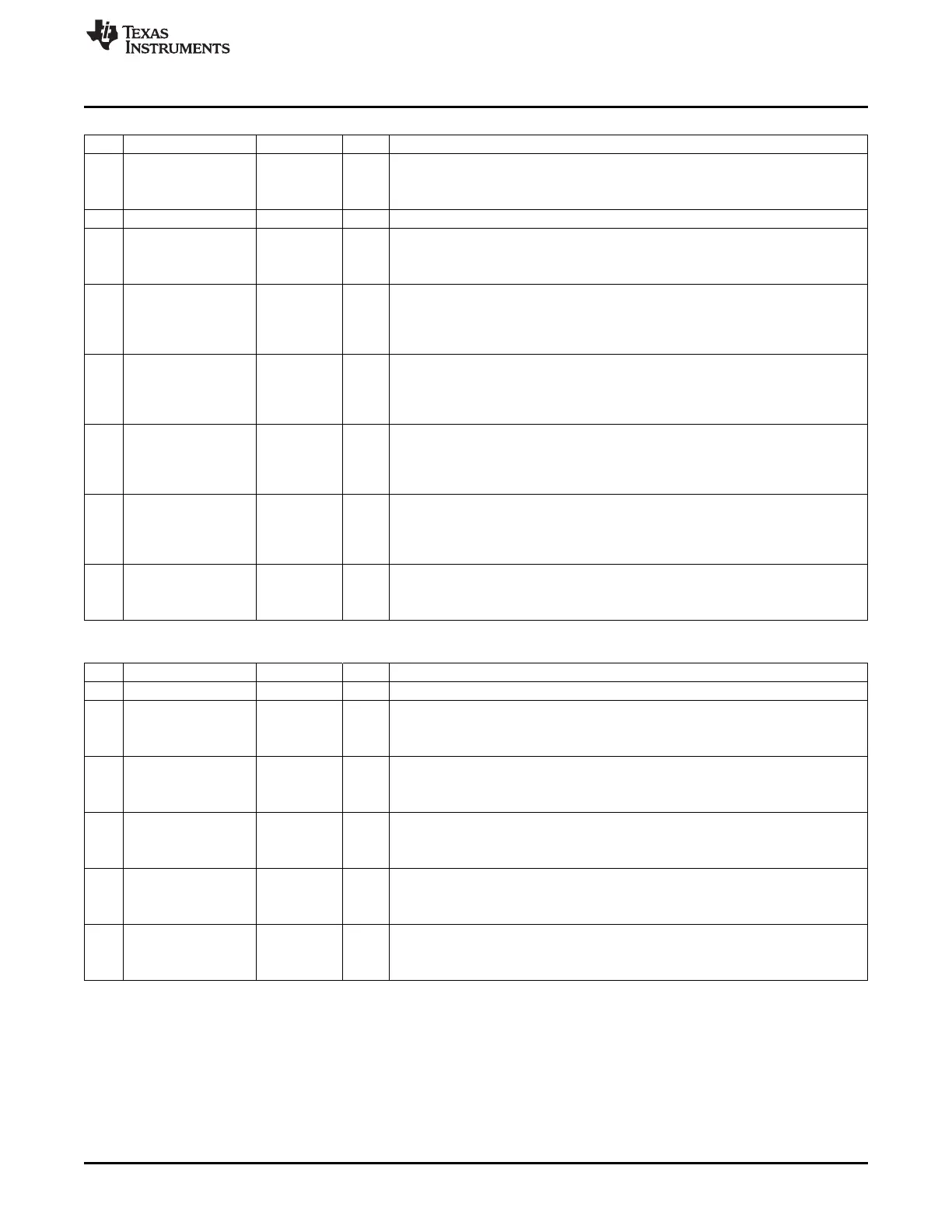

IRCON (0xC0) – Interrupt Flags 4

Bit Name Reset R/W Description

7

STIF

0 R/W Sleep Timer interrupt flag

0: Interrupt not pending

1: Interrupt pending

6 – 0 R/W Must be written 0. Writing a 1 always enables the interrupt source.

5

P0IF

0 R/W Port 0 interrupt flag

0: Interrupt not pending

1: Interrupt pending

4

T4IF

0 R/W Timer 4 interrupt flag. Set to 1 when Timer 4 interrupt occurs and cleared when CPU

H0 vectors to the interrupt service routine.

0: Interrupt not pending

1: Interrupt pending

3

T3IF

0 R/W Timer 3 interrupt flag. Set to 1 when Timer 3 interrupt occurs and cleared when CPU

H0 vectors to the interrupt service routine.

0: Interrupt not pending

1: Interrupt pending

2

T2IF

0 R/W Timer 2 interrupt flag. Set to 1 when Timer 2 interrupt occurs and cleared when CPU

H0 vectors to the interrupt service routine.

0: Interrupt not pending

1: Interrupt pending

1

T1IF

0 R/W Timer 1 interrupt flag. Set to 1 when Timer 1 interrupt occurs and cleared when CPU

H0 vectors to the interrupt service routine.

0: Interrupt not pending

1: Interrupt pending

0

DMAIF

0 R/W DMA-complete interrupt flag

0: Interrupt not pending

1: Interrupt pending

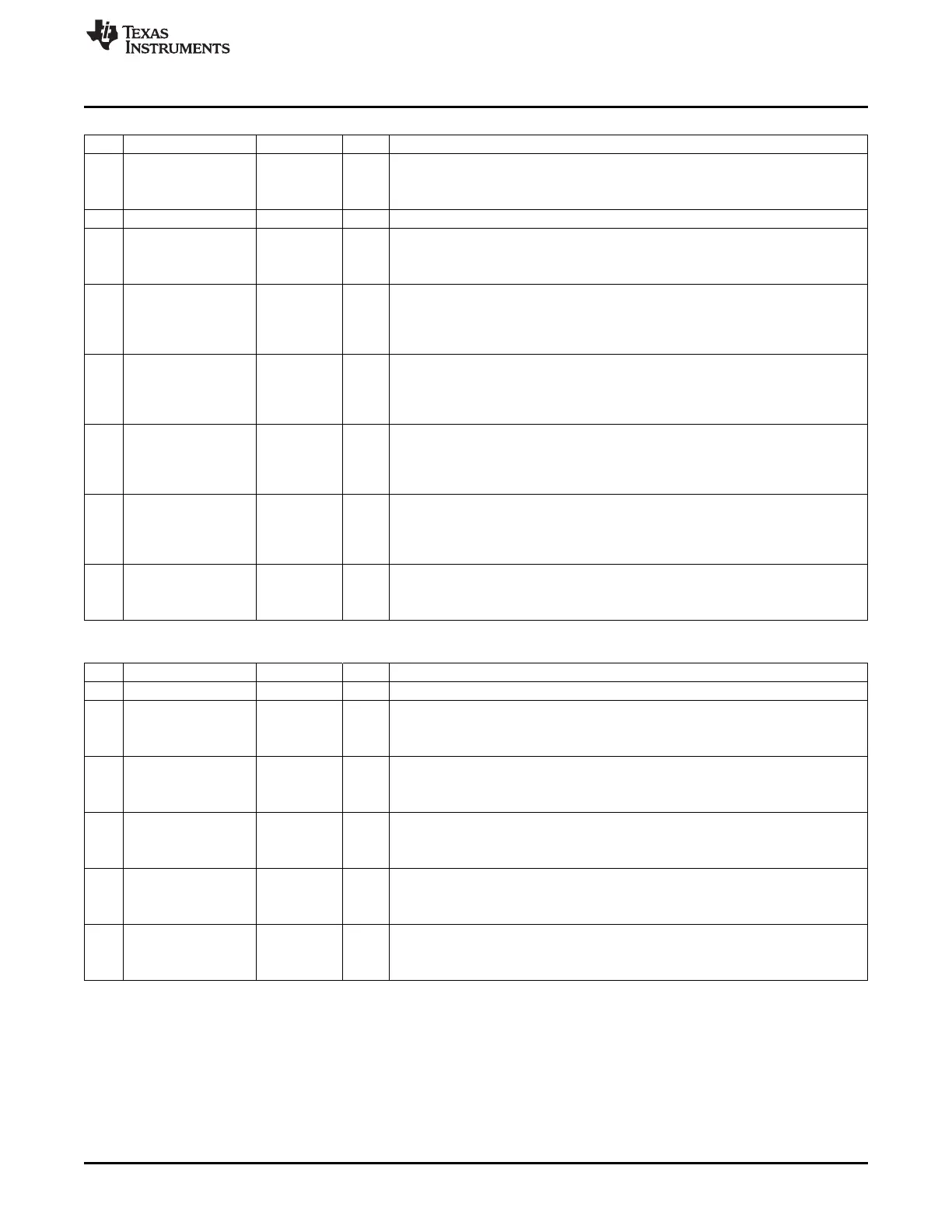

IRCON2 (0xE8) – Interrupt Flags 5

Bit Name Reset R/W Description

7:5 – 000 R/W Reserved

4

WDTIF

0 R/W Watchdog Timer interrupt flag

0: Interrupt not pending

1: Interrupt pending

3

P1IF

0 R/W Port 1 interrupt flag

0: Interrupt not pending

1: Interrupt pending

2

UTX1IF

0 R/W USART 1 TX interrupt flag

0: Interrupt not pending

1: Interrupt pending

1

UTX0IF

0 R/W USART 0 TX interrupt flag

0: Interrupt not pending

1: Interrupt pending

0

P2IF

0 R/W Port 2 interrupt flag

0: Interrupt not pending

1: Interrupt pending

2.5.3 Interrupt Priority

The interrupts are grouped into six interrupt priority groups, and the priority for each group is set by

registers IP0 and IP1. In order to assign a higher priority to an interrupt, i.e., to its interrupt group, the

corresponding bits in IP0 and IP1 must be set as shown in Table 2-6.

The interrupt priority groups with assigned interrupt sources are shown in Table 2-7. Each group is

assigned one of four priority levels. While an interrupt service request is in progress, it cannot be

interrupted by a lower- or same-level interrupt.

49

SWRU191C–April 2009–Revised January 2012 8051 CPU

Submit Documentation Feedback

Copyright © 2009–2012, Texas Instruments Incorporated

Loading...

Loading...