www.ti.com

Timer 2 Registers

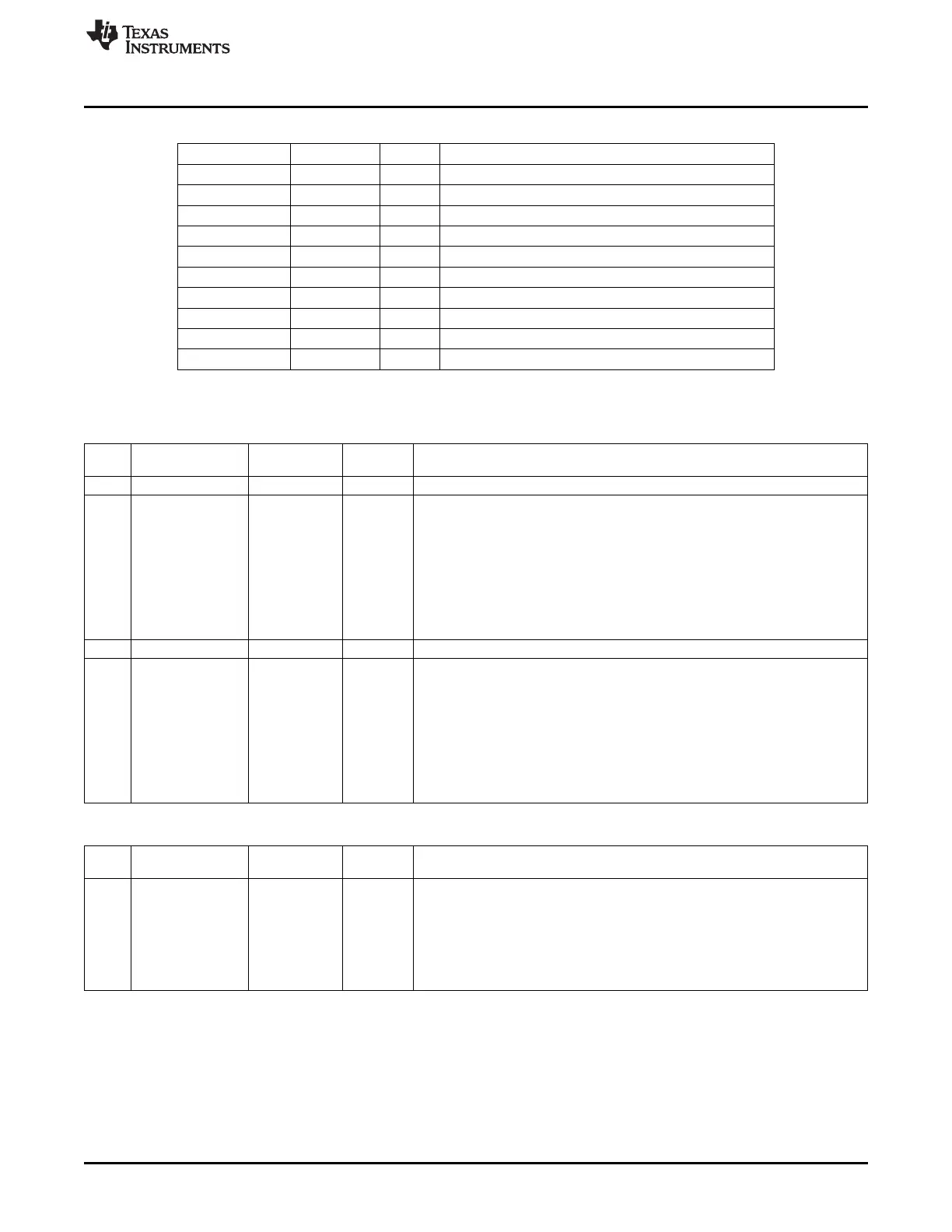

Table 22-1. Internal Registers

Register Name Reset R/W Function

t2tim[15:0] 0x0000 R/W Holds the 16-bit upcounter

t2_cap[15:0] 0x0000 R Holds the last captured value of the upcounter

t2_per[15:0] 0x0000 R/W Holds the period of the upcounter

t2_cmp1[15:0] 0x0000 R/W Holds compare value 1 for the upcounter

t2_cmp2[15:0] 0x0000 R/W Holds compare value 2 for the upcounter

t2ovf[23:0] 0x00 0000 R/W Holds the 24-bit overflow counter

t2ovf_cap[23:0] 0x00 0000 R Holds the last captured value of the overflow counter

t2ovf_per[23:0] 0x00 0000 R/W Holds the period of the overflow counter

t2ovf_cmp1[23:0] 0x00 0000 R/W Holds compare value 1 for the overflow counter

t2ovf_cmp2[23:0] 0x00 0000 R/W Holds compare value 2 for the overflow counter

The registers listed in the remainder of this section are directly accessible in the SFR address space.

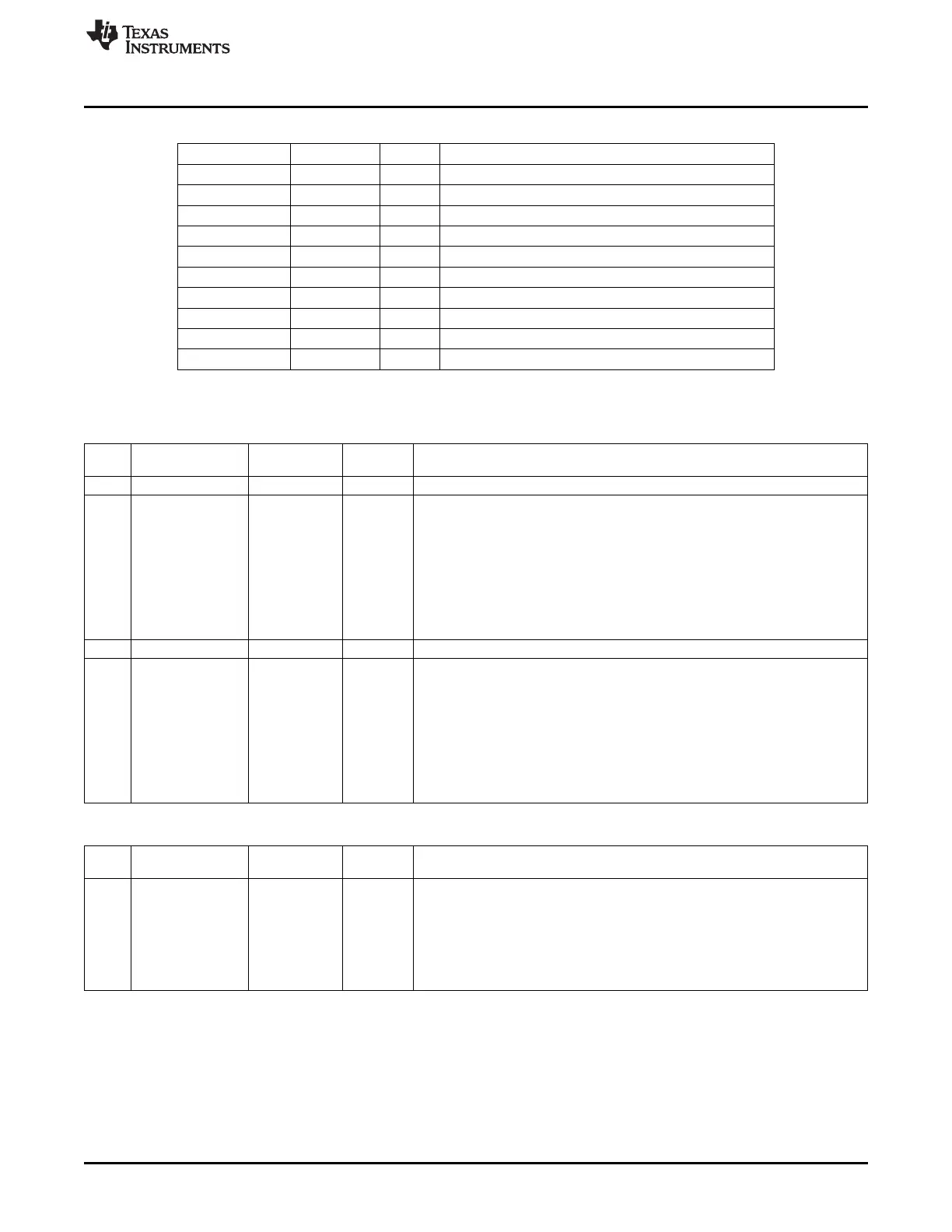

T2MSEL (0xC3) – Timer 2 Multiplex Select

Bit Name Reset R/W Function

No.

7:0 – 0 R0 Reserved. Read as 0

6:4

T2MOVFSEL

0 R/W The value of this register selects the internal registers that are modified or read

when accessing T2MOVF0, T2MOVF1, and T2MOVF2.

000: t2ovf (overflow counter)

001: t2ovf_cap (overflow capture)

010: t2ovf_per (overflow period)

011: t2ovf_cmp1 (overflow compare 1)

100: t2ovf_cmp2 (overflow compare 2)

101 to 111: Reserved

3 – 0 R0 Reserved. Read as 0

2:0

T2MSEL

0 R/W The value of this register selects the internal registers that are modified or read

when accessing T2M0 and T2M1.

000: t2tim (timer count value)

001: t2_cap (timer capture)

010: t2_per (timer period)

011: t2_cmp1 (timer compare 1)

100: t2_cmp2 (timer compare 2)

101 to 111: Reserved

T2M0 (0xA2) – Timer 2 Multiplexed Register 0

Bit Name Reset R/W Function

No.

7:0

T2M0

0 R/W Indirectly returns/modifies bits [7:0] of an internal register depending on the

T2MSEL.T2MSEL value.

When reading the T2M0 register with T2MSEL.T2MSEL set to 000 and

T2CTRL.LATCH_MODE set to 0, the timer (t2tim) value is latched.

When reading the T2M0 register with T2MSEL.T2MSEL set to 000 and

T2CTRL.LATCH_MODE set to 1, the timer (t2tim) and overflow counter (t2ovf)

values are latched.

213

SWRU191C–April 2009–Revised January 2012 Timer 2 (MAC Timer)

Submit Documentation Feedback

Copyright © 2009–2012, Texas Instruments Incorporated

Loading...

Loading...