AES Registers

www.ti.com

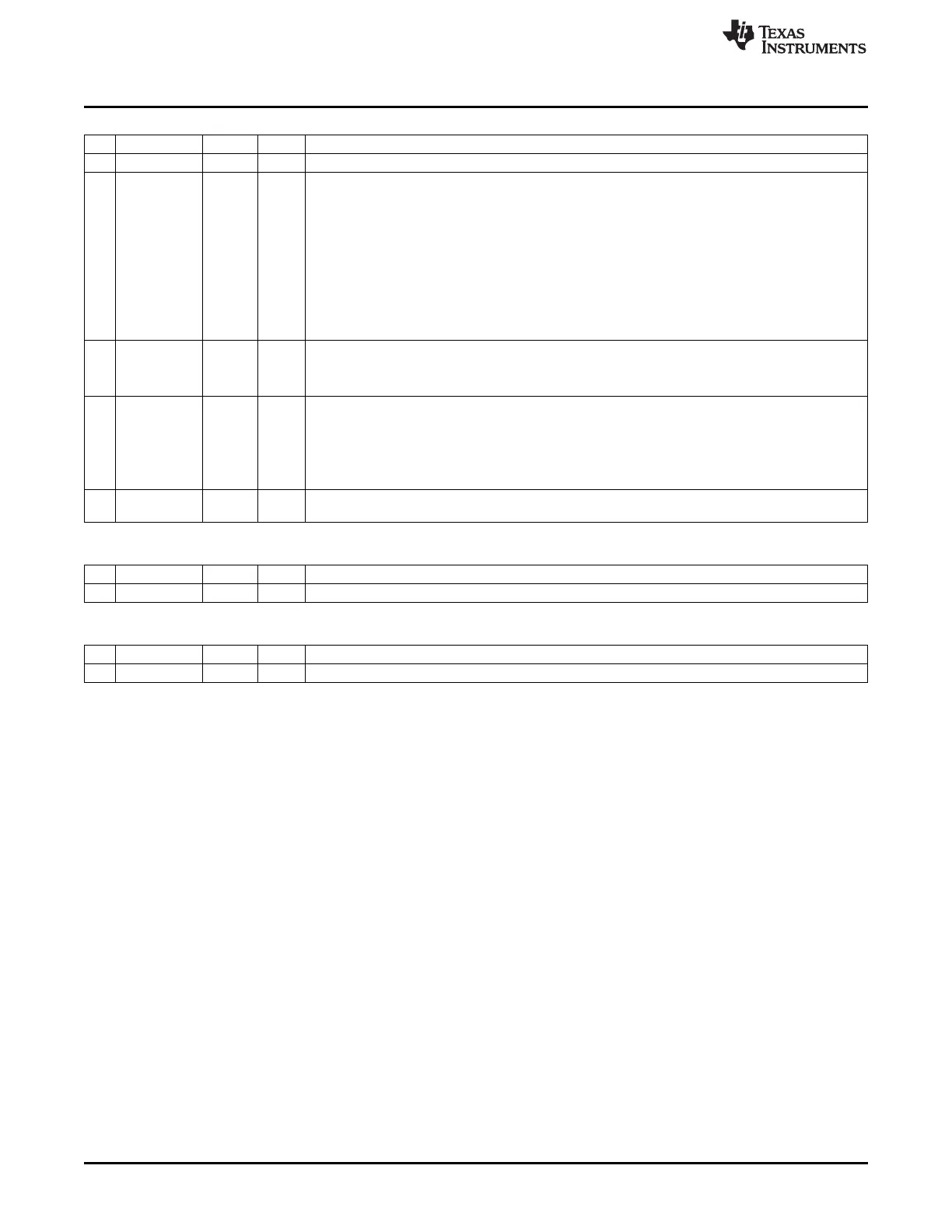

ENCCS (0xB3) – Encryption Control and Status

Bit Name Reset R/W Description

7 – 0 R0 Reserved, always read as 0

6:4

MODE[2:0]

000 R/W Encryption/decryption mode

000: CBC

001: CFB

010: OFB

011: CTR

100: ECB

101: CBC MAC

110: Reserved

111: Reserved

3

RDY

1 R Encryption/decryption ready status

0: Encryption/decryption in progress

1: Encryption/decryption is completed.

2:1

CMD[1:0]

0 R/W

Command to be performed when a 1 is written to ST

00: Encrypt block

01: Decrypt block

10: Load key

11: Load IV/nonce

0 0 R/W1 Start processing command set by CMD. Must be issued for each command or 128-bit block of data.

ST

H0 Cleared by hardware.

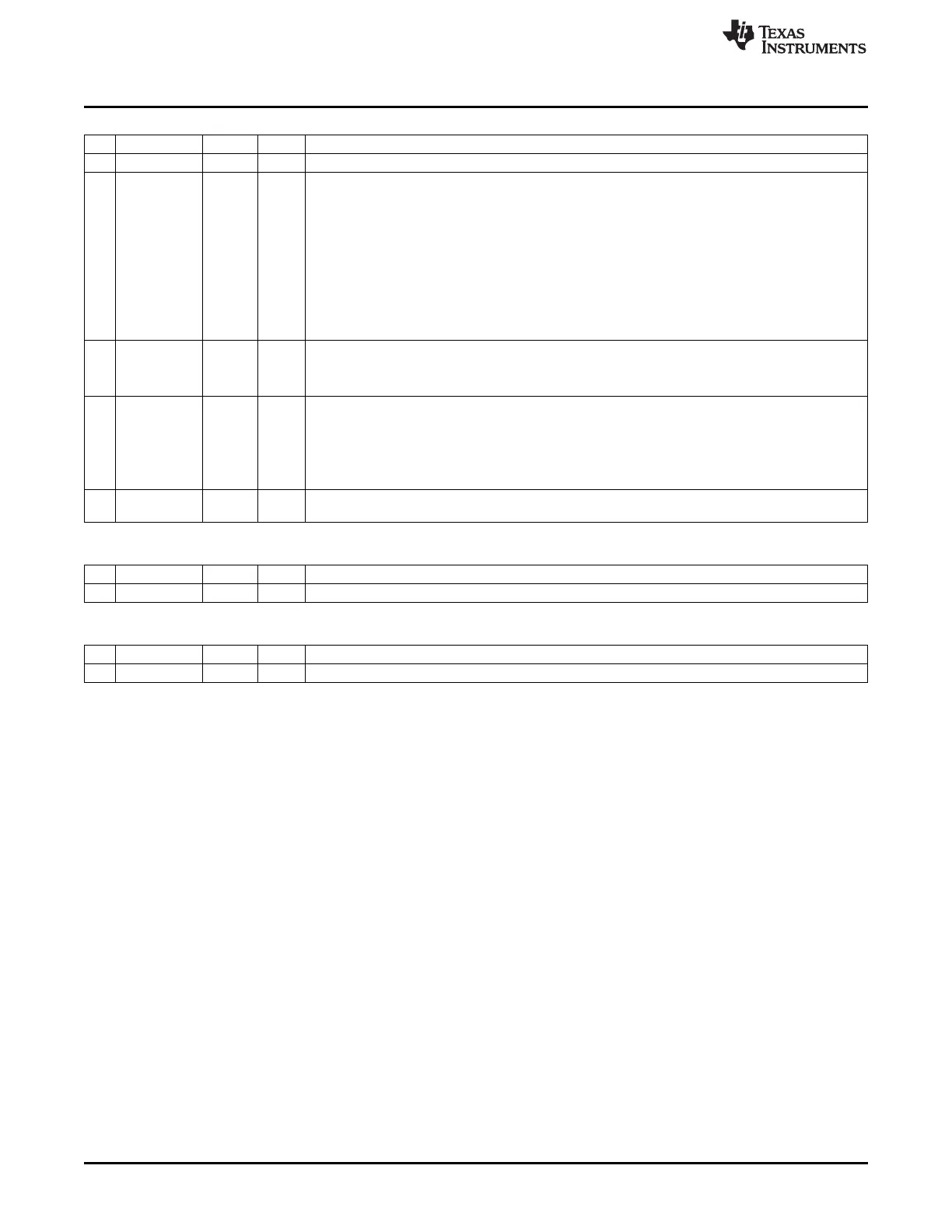

ENCDI (0xB1) – Encryption Input Data

Bit Name Reset R/W Description

7:0

DIN[7:0]

0x00 R/W Encryption input data

ENCDO (0xB2) – Encryption Output Data

Bit Name Reset R/W Description

7:0

DOUT[7:0]

0x00 R/W Encryption output data

158

AES Coprocessor SWRU191C–April 2009–Revised January 2012

Submit Documentation Feedback

Copyright © 2009–2012, Texas Instruments Incorporated

Loading...

Loading...