Bit-Stream Processor

www.ti.com

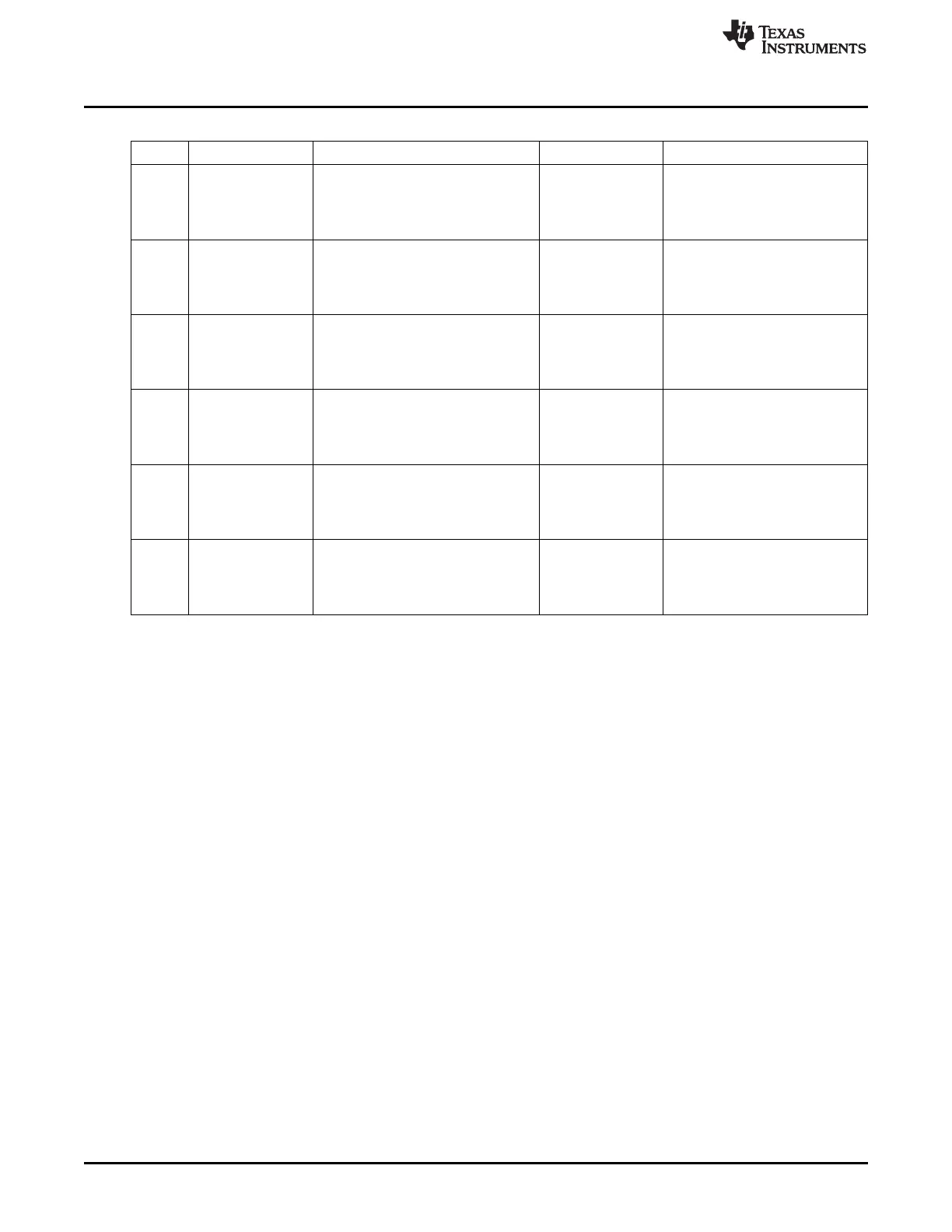

Table 25-9. Register Settings for Some Commonly Used CRCs, Assuming Initialization With All 1s

Order CRC

PRF_CRC_LEN BSP_Px PRF_CRC_INIT

BSP_P0 = 0x00 PRF_CRC_INIT[0] = 0x00

BSP_P1 = 0x00 PRF_CRC_INIT[1] = 0x00

8 1 CRC-8-ATM x

8

+ x

2

+ x + 1

BSP_P2 = 0x00 PRF_CRC_INIT[2] = 0x00

BSP_P3 = 0x07 PRF_CRC_INIT[3] = 0xFF

BSP_P0 = 0x00 PRF_CRC_INIT[0] = 0x00

BSP_P1 = 0x00 PRF_CRC_INIT[1] = 0x00

8 1 CRC-8 x

8

+ x

7

+ x

6

+ x

4

+ x

2

+ 1

BSP_P2 = 0x00 PRF_CRC_INIT[2] = 0x00

BSP_P3 = 0xD3 PRF_CRC_INIT[3] = 0xFF

BSP_P0 = 0x00 PRF_CRC_INIT[0] = 0x00

CRC-16 (used in CC2500) x

16

+ x

15

+

BSP_P1 = 0x00 PRF_CRC_INIT[1] = 0x00

16 2

x

2

+ 1

BSP_P2 = 0x05 PRF_CRC_INIT[2] = 0xFF

BSP_P3 = 0x80 PRF_CRC_INIT[3] = 0xFF

BSP_P0 = 0x00 PRF_CRC_INIT[0] = 0x00

BSP_P1 = 0x00 PRF_CRC_INIT[1] = 0x00

16 2 CRC-16-CCITT x

16

+ x

12

+ x

5

+ 1

BSP_P2 = 0x21 PRF_CRC_INIT[2] = 0xFF

BSP_P3 = 0x10 PRF_CRC_INIT[3] = 0xFF

BSP_P0 = 0x00 PRF_CRC_INIT[0] = 0x00

CRC-24 x

24

+ x

22

+ x

20

+ x

19

+ x

18

+ x

16

BSP_P1 = 0xCB PRF_CRC_INIT[1] = 0xFF

24 3 + x

14

+ x

13

+ x

11

+ x

10

+ x

8

+ x

7

+ x

6

+ x

3

BSP_P2 = 0x6D PRF_CRC_INIT[2] = 0xFF

+ x + 1

BSP_P3 = 0x5D PRF_CRC_INIT[3] = 0xFF

BSP_P0 = 0xB7 PRF_CRC_INIT[0] = 0xFF

CRC-32-IEEE 802.3 x

32

+ x

26

+ x

23

+

BSP_P1 = 0x1D PRF_CRC_INIT[1] = 0xFF

32 4 x

22

+ x

16

+ x

12

+ x

11

+ x

10

+ x

8

+ x

7

+ x

5

BSP_P2 = 0xC1 PRF_CRC_INIT[2] = 0xFF

+ x

4

+ x

2

+ x + 1

BSP_P3 = 0x04 PRF_CRC_INIT[3] = 0xFF

25.4.4 Coprocessor Mode

The coprocessor mode is used to run the BSP as a stand-alone and not part of the signal path. It must not

be used while the LLE is running. Coprocessor mode is selected by setting BSP_MODE.CP_MODE to 01 or

11. In these modes, one byte to be processed is written to the BSP_DATA register, and the result of

processing this byte can later be read back from the same register. When BSP_MODE.CP_MODE is 01, the

coprocessor is in receive mode, where the whitener is applied before the CRC. When

BSP_MODE.CP_MODE is 11, the coprocessor is in transmit mode, where the whitener is applied after the

CRC.

To apply the BSP operations to a byte, write it to the BSP_DATA register. When this register is written to,

the BSP_MODE.CP_BUSY bit goes high.

If CP_MODE.CP_END is 0, the first bit provided is the LSB and the last bit is the MSB. If CP_MODE.CP_END

is 1, the first bit provided is the MSB and the last bit is the LSB.

When BSP_MODE.CP_BUSY goes low, the processed data can be read from the BSP_DATA register. If one

or both whiteners are enabled, this byte is whitened or de-whitened. Otherwise, it is the same as the byte

written, except if the CRC is being read as described in the following text.

To read out a CRC in transmit mode, set BSP_MODE.CP_READOUT to 1. A zero must be written to the

BSP_DATA register, and when BSP_MODE.CP_BUSY goes low, a CRC byte can be read from BSP_DATA.

This should be repeated for each CRC byte. If whitening is enabled, the read back CRC bytes are

whitened.

The BSP must not be set in coprocessor mode while the LLE is processing a packet.

308

CC2541 Proprietary Mode Radio SWRU191C– April 2009–Revised January 2012

Submit Documentation Feedback

Copyright © 2009–2012, Texas Instruments Incorporated

Loading...

Loading...