Registers

www.ti.com

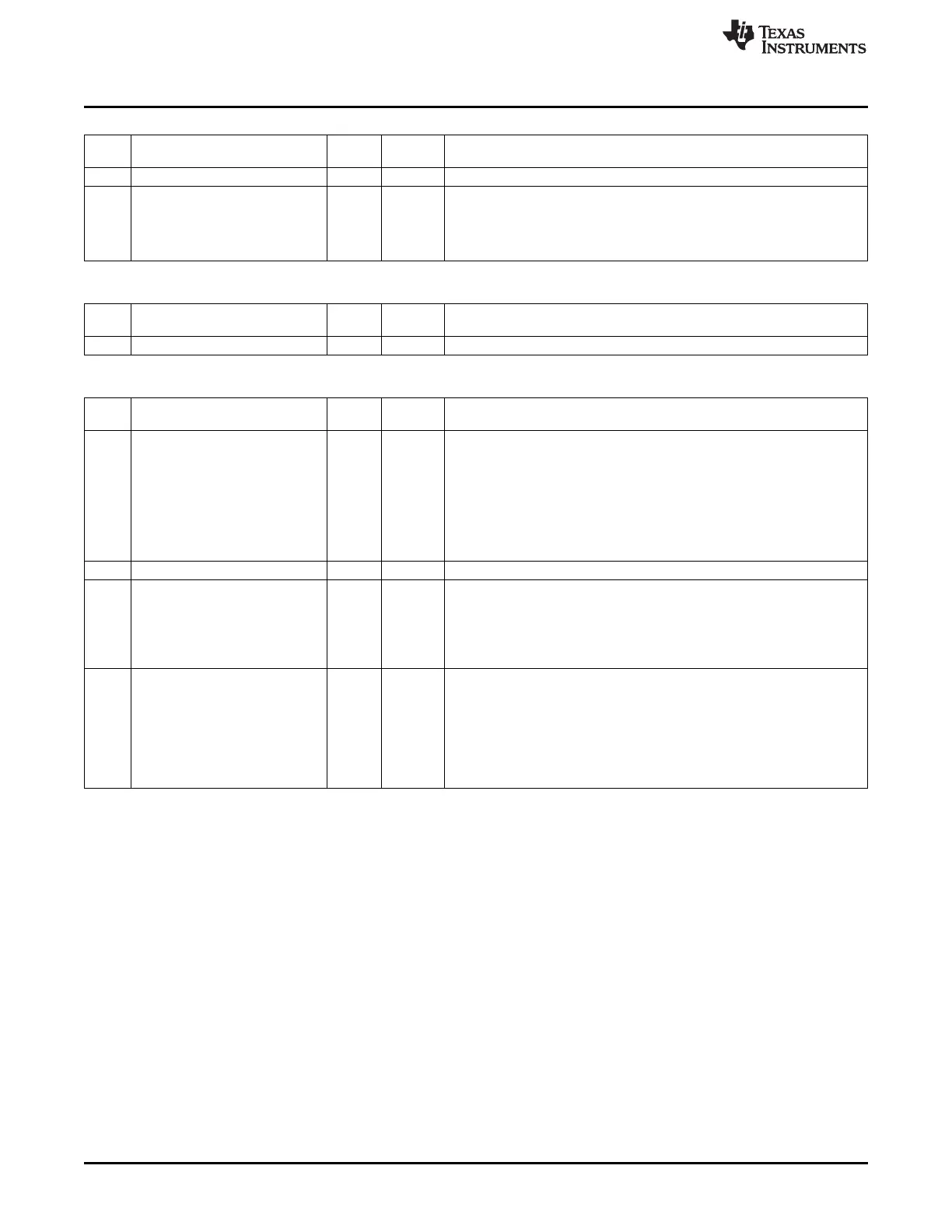

AAFGAIN (0x61A1) – AAF Gain Setting

Bit

Name Reset R/W Description

No.

7:2 – 0000 00 R0 Reserved. Read as zero

1:0

AAF_GAIN[1:0]

11 R/W Controls attenuation in AAF

00: 9-dB attenuation in AAF

01: 6-dB attenuation in AAF

10: 3-dB attenuation in AAF

11: 0-dB attenuation in AAF (reference level)

ADCTEST0 (0x61A2) – ADC Tuning

Bit

Name Reset R/W Description

No.

7:0

ADC_ADJ[7:0]

0x10 R/W Adjust ADC gain

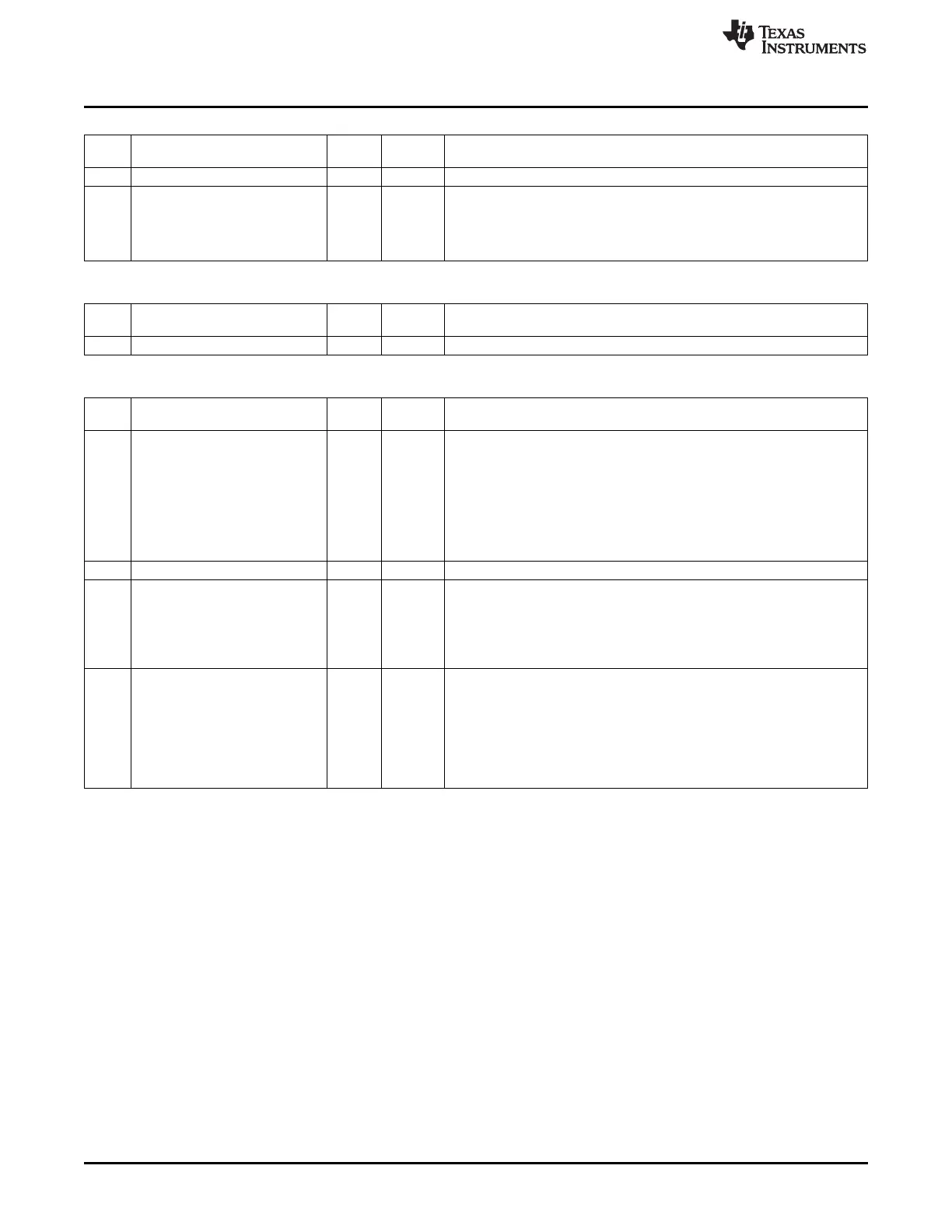

MDMTEST0 (0x61A5) – Modem Configuration

Bit

Name Reset R/W Description

No.

7:5

RSSI_ACC[2:0]

101 R/W RSSI accuracy

000: 5.33-µs average window

001: Mean of two 5.33-µs average windows

010: Reserved

011: Mean of four 5.33-µs average windows

100: 21.3-µs average window

101: Mean of two 21.3-µs average windows

110: Reserved

111: Mean of four 21.3-µs average windows

4 – 0 R/W Reserved, always write 0.

3:2

DC_BLOCK_LENGTH[1:0]

00 R/W Controls the number of samples to be accumulated between each dump of

the accumulate-and-dump filter used in dc removal.

00: 16 samples

01: 32 samples

10: 64 samples

11: 128 samples

1:0

DC_BLOCK_MODE[1:0]

01 R/W Selects the mode of operation:

00 : Manual override mode

01 : Enable dc cancellation. Normal operation

10 : Freeze estimates of dc when sync is found. Start estimating dc again

when searching for the next frame.

11 : Delayed dc offset estimate used. Delay set by

MDMTEST1.DC_DELAY. Until the first estimate is ready, the manual

override value is used.

344

CC2541 Proprietary Mode Radio SWRU191C– April 2009–Revised January 2012

Submit Documentation Feedback

Copyright © 2009–2012, Texas Instruments Incorporated

Loading...

Loading...