www.ti.com

Interrupts

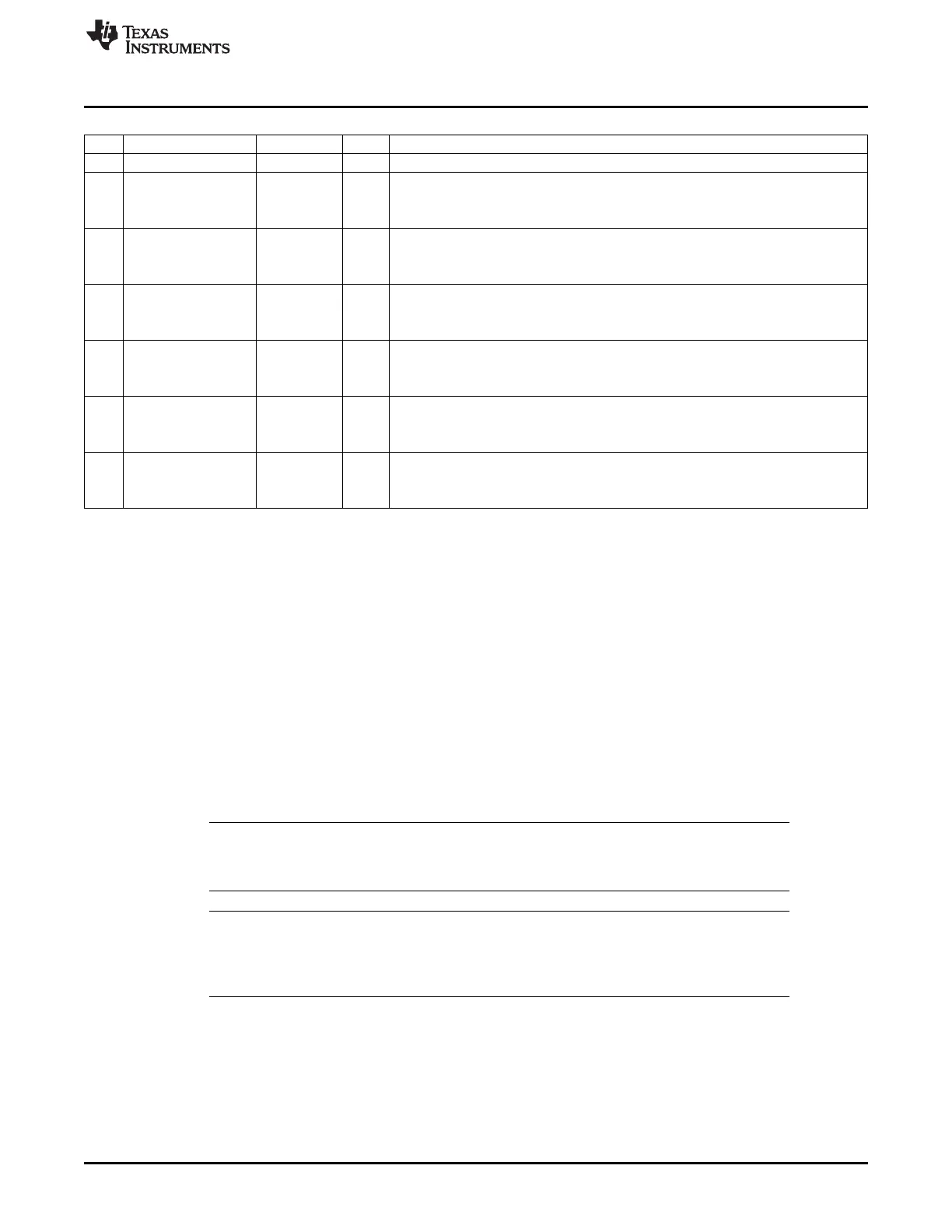

IEN2 (0x9A) – Interrupt Enable 2

Bit Name Reset R/W Description

7:6 – 00 R0 Reserved. Read as 0

5

WDTIE

0 R/W Watchdog Timer interrupt enable

0: Interrupt disabled

1: Interrupt enabled

4

P1IE

0 R/W Port 1 interrupt enable

0: Interrupt disabled

1: Interrupt enabled

3

UTX1IE

0 R/W USART 1 TX interrupt enable

0: Interrupt disabled

1: Interrupt enabled

2

UTX0IE

0 R/W USART 0 TX interrupt enable

0: Interrupt disabled

1: Interrupt enabled

1

P2IE

0 R/W Port 2 and USB interrupt enable

0: Interrupt disabled

1: Interrupt enabled

0

RFIE

0 R/W RF general interrupt enable

0: Interrupt disabled

1: Interrupt enabled

2.5.2 Interrupt Processing

When an interrupt occurs, the CPU vectors to the interrupt-vector address as shown in Table 2-5. Once an

interrupt service has begun, it can be interrupted only by a higher-priority interrupt. The interrupt service is

terminated by an RETI (return-from-interrupt instruction). When an RETI is performed, the CPU returns to

the instruction that would have been next when the interrupt occurred.

When the interrupt condition occurs, the CPU also indicates this by setting an interrupt flag bit in the

interrupt flag registers. This bit is set regardless of whether the interrupt is enabled or disabled. If the

interrupt is enabled when an interrupt flag is set, then on the next instruction cycle, the interrupt is

acknowledged by hardware, forcing an LCALL to the appropriate vector address.

Interrupt response requires a varying amount of time, depending on the state of the CPU when the

interrupt occurs. If the CPU is performing an interrupt service with equal or greater priority, the new

interrupt is pending until it becomes the interrupt with highest priority. In other cases, the response time

depends on current instruction. The fastest possible response to an interrupt is seven machine cycles.

This includes one machine cycle for detecting the interrupt and six cycles to perform the LCALL.

NOTE: If an interrupt is disabled and the interrupt flag is polled, the 8051 assembly instruction JBC

must not be used to poll the interrupt flag and clear it when set. If the JBC instruction is

used, the interrupt flag may be re-asserted immediately.

NOTE: If the assembly instruction XCH A, IEN0 is used to clear the global interrupt enable flag

EA, the CPU may enter the interrupt routine on the cycle following this instruction. If that

happens, the interrupt routine is executed with EA set to 0, which may delay the service of

higher-priority interrupts.

47

SWRU191C–April 2009–Revised January 2012 8051 CPU

Submit Documentation Feedback

Copyright © 2009–2012, Texas Instruments Incorporated

Loading...

Loading...