Interrupts

www.ti.com

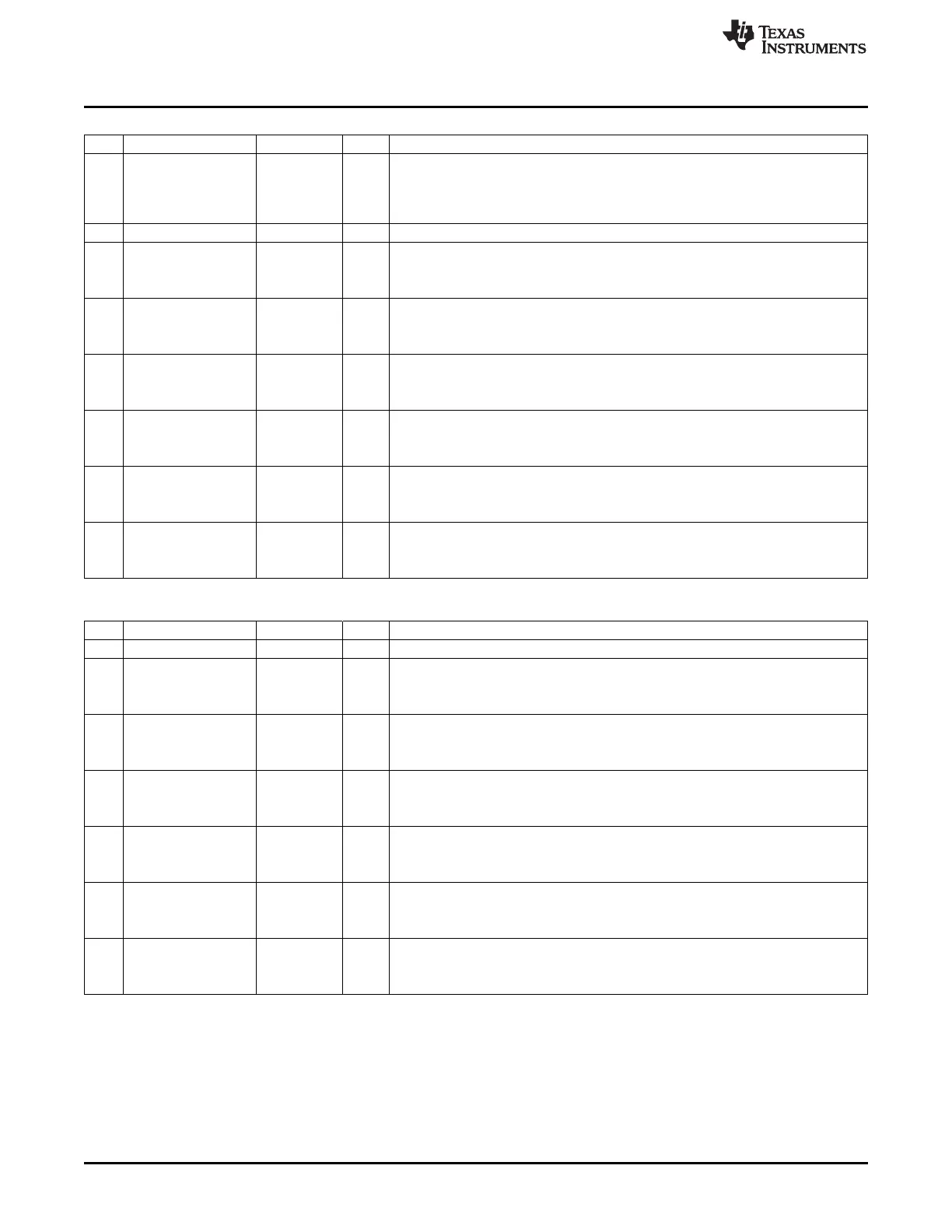

IEN0 (0xA8) – Interrupt Enable 0

Bit Name Reset R/W Description

7

EA

0 R/W Disables all interrupts.

0: No interrupt is acknowledged.

1: Each interrupt source is individually enabled or disabled by setting its

corresponding enable bit.

6 – 0 R0 Reserved. Read as 0

5

STIE

0 R/W Sleep Timer interrupt enable

0: Interrupt disabled

1: Interrupt enabled

4

ENCIE

0 R/W AES encryption/decryption interrupt enable

0: Interrupt disabled

1: Interrupt enabled

3

URX1IE

0 R/W USART 1 RX interrupt enable

0: Interrupt disabled

1: Interrupt enabled

2

URX0IE

0 R/W USART0 RX interrupt enable

0: Interrupt disabled

1: Interrupt enabled

1

ADCIE

0 R/W ADC interrupt enable

0: Interrupt disabled

1: Interrupt enabled

0

RFERRIE

0 R/W RF core error interrupt enable

0: Interrupt disabled

1: Interrupt enabled

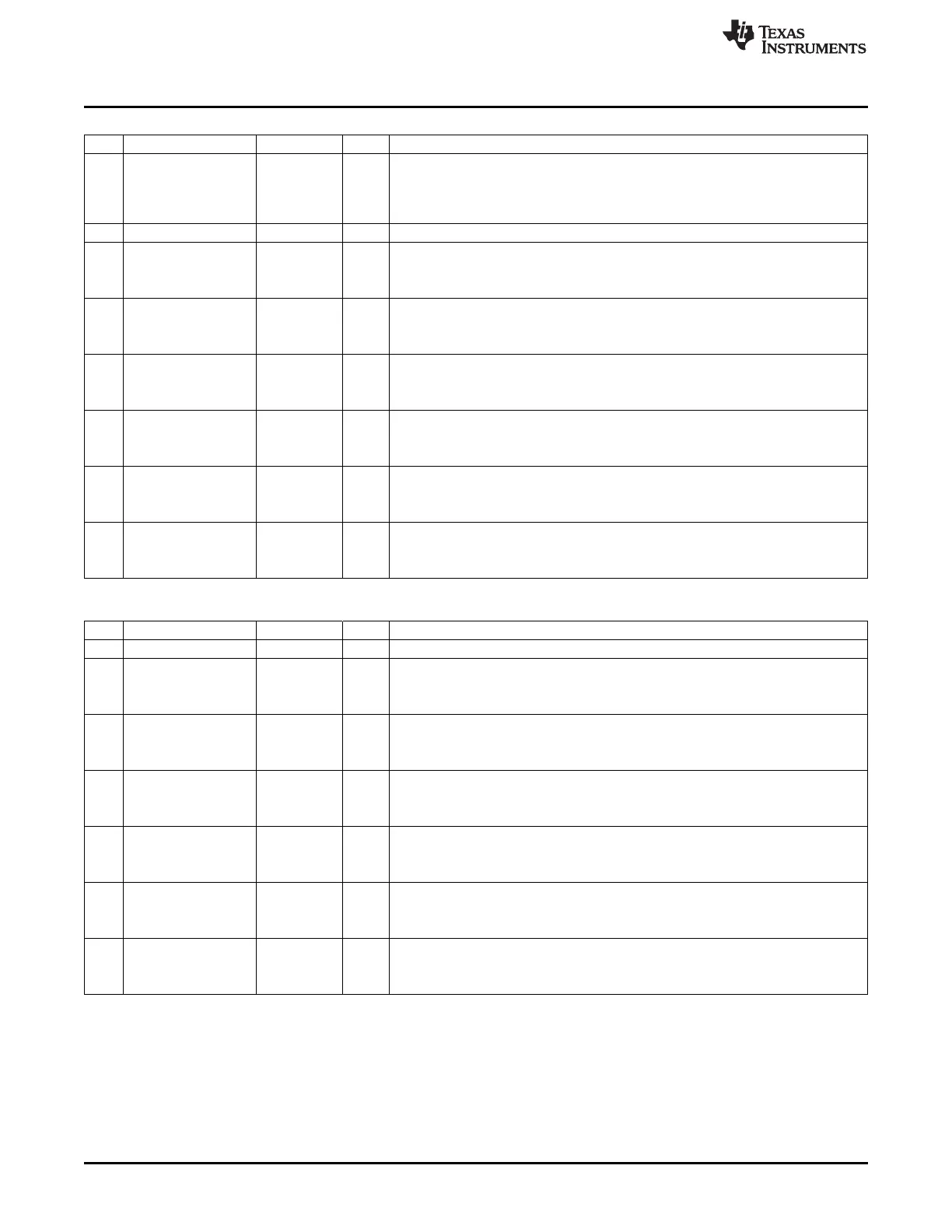

IEN1 (0xB8) – Interrupt Enable 1

Bit Name Reset R/W Description

7:6 – 00 R0 Reserved. Read as 0

5

P0IE

0 R/W Port 0 interrupt enable

0: Interrupt disabled

1: Interrupt enabled

4

T4IE

0 R/W Timer 4 interrupt enable

0: Interrupt disabled

1: Interrupt enabled

3

T3IE

0 R/W Timer 3 interrupt enable

0: Interrupt disabled

1: Interrupt enabled

2

T2IE

0 R/W Timer 2 interrupt enable

0: Interrupt disabled

1: Interrupt enabled

1

T1IE

0 R/W Timer 1 interrupt enable

0: Interrupt disabled

1: Interrupt enabled

0

DMAIE

0 R/W DMA transfer interrupt enable

0: Interrupt disabled

1: Interrupt enabled

46

8051 CPU SWRU191C–April 2009–Revised January 2012

Submit Documentation Feedback

Copyright © 2009–2012, Texas Instruments Incorporated

Loading...

Loading...