www.ti.com

RF Core

The interrupt-enable bits in the mask registers are used to enable individual interrupt sources for the two

RF interrupts. Note that masking an interrupt source does not affect the updating of the status in the flag

registers.

Due to the use of individual interrupt masks in the RF Core, the interrupts coming from RF Core have

two-layered masking, and care must be taken when processing these interrupts. The procedure is

described as follows.

To clear an interrupt from the RF Core, one must clear two flags, both the flag set in RF Core and the one

set in S1CON or TCON (depending on which interrupt is triggered). If a flag is cleared in the RF Core and

there are other unmasked flags standing, another interrupt is generated.

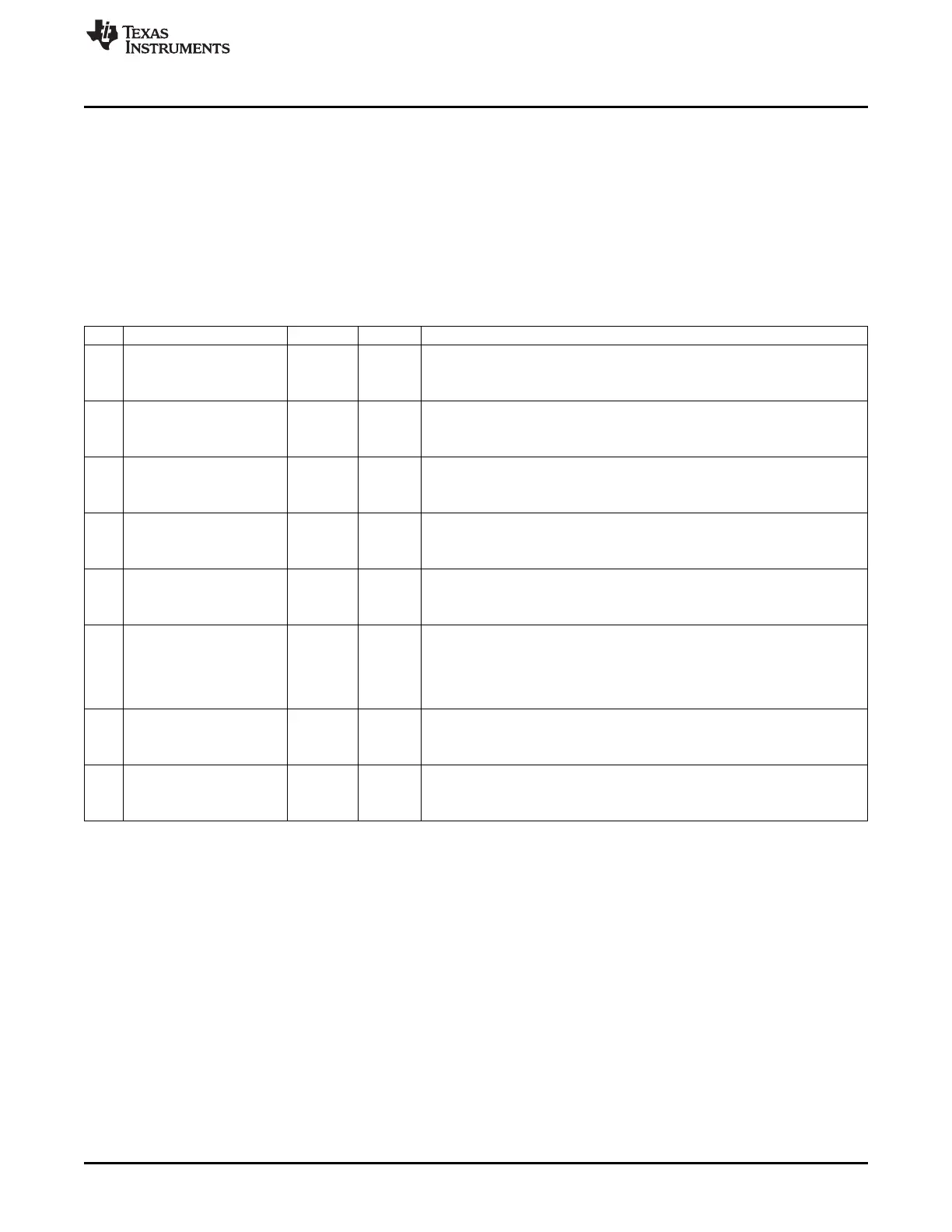

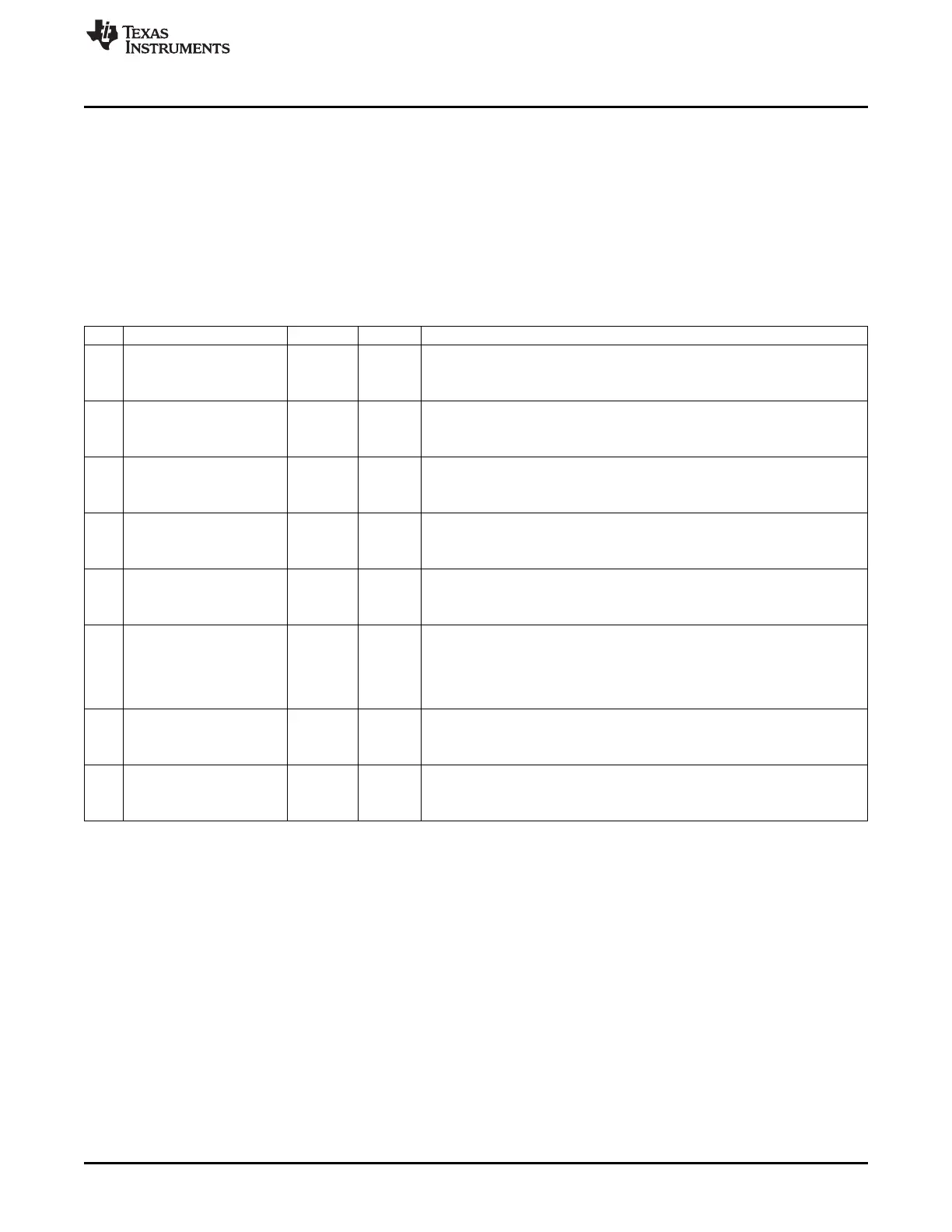

RFIRQF0 (0xE9) RF Interrupt Flags

Bit Name Reset R/W Description

7

RXMASKZERO

0 R/W0

The RXENABLE register has gone from a nonzero state to an all-zero state.

0: No interrupt pending

1: Interrupt pending

6

RXPKTDONE

0 R/W0 A complete frame has been received.

0: No interrupt pending

1: Interrupt pending

5

FRAME_ACCEPTED

0 R/W0 Frame has passed frame filtering.

0: No interrupt pending

1: Interrupt pending

4

SRC_MATCH_FOUND

0 R/W0 Source match found

0: No interrupt pending

1: Interrupt pending

3

SRC_MATCH_DONE

0 R/W0 Source matching complete

0: No interrupt pending

1: Interrupt pending

2

FIFOP

0 R/W0 The number of bytes in the RXFIFO is above the threshold. Also raised when

a complete frame has been received, and when a packet has been read out

completely and there are more complete packets available.

0: No interrupt pending

1: Interrupt pending

1

SFD

0 R/W0 SFD has been received or transmitted.

0: No interrupt pending

1: Interrupt pending

0

ACT_UNUSED

0 R/W0 Reserved

0: No interrupt pending

1: Interrupt pending

221

SWRU191C–April 2009–Revised January 2012 CC253x Radio

Submit Documentation Feedback

Copyright © 2009–2012, Texas Instruments Incorporated

Loading...

Loading...