www.ti.com

Registers

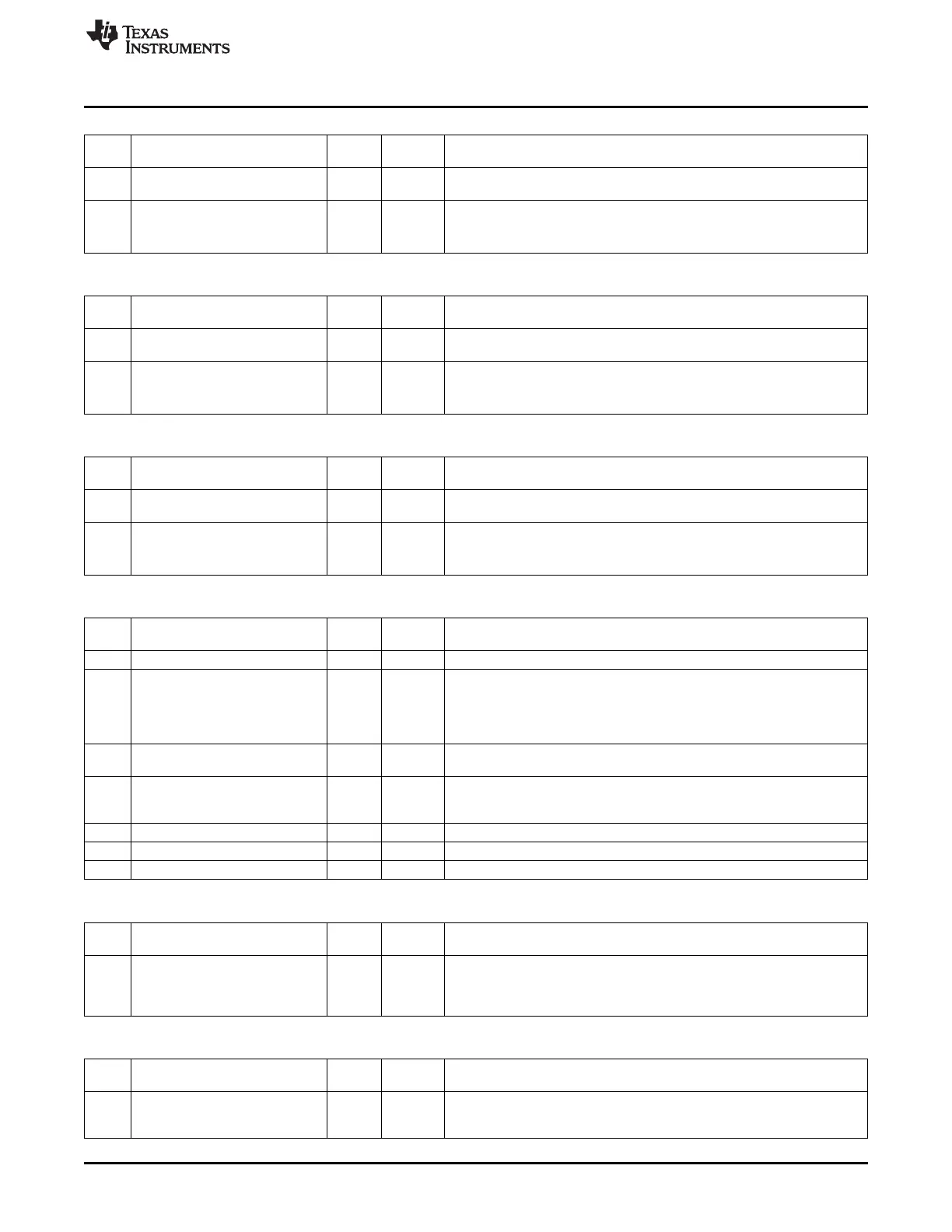

SEMAPHORE0 (0x618A) – Semaphore for Accessing RF Data Memory

Bit

Name Reset R/W Description

No.

7:1 – 0000 R0 Reserved, read as 0

000

0

SEMAPHORE

1 R/W1

When SEMAPHORE = 1 and SEMAPHORE0 is read, SEMAPHORE is

set to 0. SEMAPHORE can only be set to 1 by a reset or by writing 1 to

it.

SEMAPHORE1 (0x618B) – Semaphore for Accessing RF Data Memory

Bit

Name Reset R/W Description

No.

7:1 – 0000 R0 Reserved, read as 0

000

0

SEMAPHORE

1 R/W1

When SEMAPHORE = 1 and SEMAPHORE1 is read, SEMAPHORE is

set to 0. SEMAPHORE can only be set to 1 by a reset or by writing 1 to

it.

SEMAPHORE2 (0x618C) – Semaphore

Bit

Name Reset R/W Description

No.

7:1 – 0000 R0 Reserved, read as 0

000

0 1 R/W1

SEMAPHORE When SEMAPHORE = 1 and SEMAPHORE2 is read, SEMAPHORE is

set to 0. SEMAPHORE can only be set to 1 by a reset or by writing 1 to

it.

RFSTAT (0x618D) – RF Core Status

Bit

Name Reset R/W Description

No.

7

MOD_UNDERFLOW

0 R/W0 Modulator has underflowed. Must be cleared by software

6:5

DEM_STATUS

00 R Demodulator status

00: Idle

01: Active

10: Finishing

11: Error

4

SFD

0 R High when the sync word has been sent in TX or when sync has been

obtained in RX

3

CAL_RUNNING

0 R Frequency synthesizer calibration status.

0: Calibration done or not started

1: Calibration in progress.

2

LOCK_STATUS

0 R 1 when PLL is in lock; 0 otherwise

1

TX_ACTIVE

0 R Status signal, active when the LLE is in one of the transmit states

0

RX_ACTIVE

0 R Status signal, active when the LLE is in one of the receive states

RSSI (0x618E) – Received Signal Strength Indicator

Bit

Name Reset R/W Description

No.

7:0

RSSI_VAL[7:0]

0x80 R RSSI estimate on a logarithmic scale. Unit is 1 dB; offset depends on the

gain of the Rx chain, including external components; see the device data

sheet. The reset value of 0x80 also indicates that the RSSI value is

invalid/measurement not yet complete.

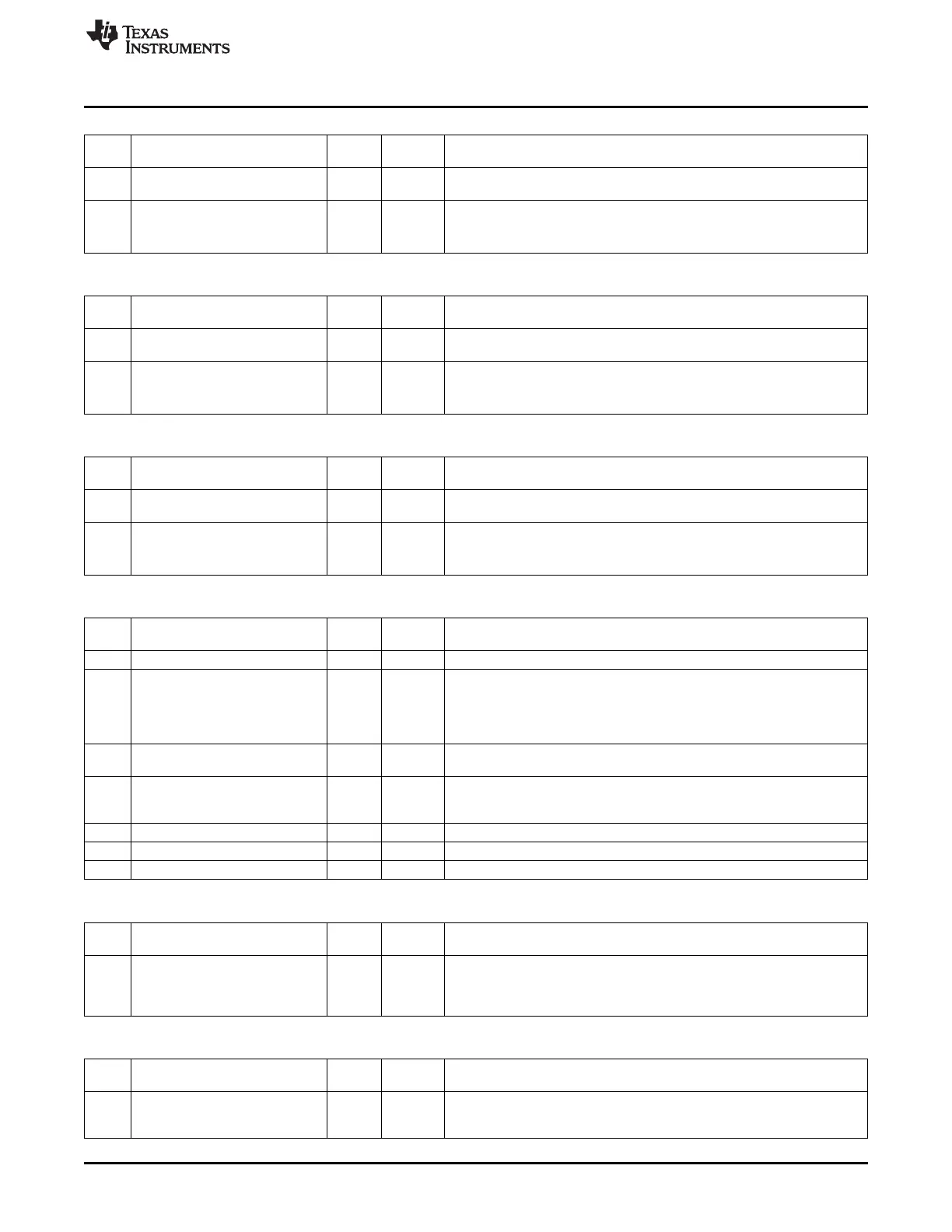

RFPSRND (0x618F) – Pseudorandom Number Generator

Bit

Name Reset R/W Description

No.

7:0

RNG_DOUT[7:0]

0x00 R The value read from the pseudorandom number generator, see

Chapter 14. Reading this register generates causes the shift register to be

updated with 13 times rollout.

339

SWRU191C–April 2009–Revised January 2012 CC2541 Proprietary Mode Radio

Submit Documentation Feedback

Copyright © 2009–2012, Texas Instruments Incorporated

Loading...

Loading...