4.4.6 [130] D-Flip-Flop, Master

Type Function

Type Function

I1

b C, Clock

O1

b output O1

I2

b D, Data input

O2

b

negated output O2 =

1O

I3

b Master Set input

P1

I4

b Master Reset input

P2

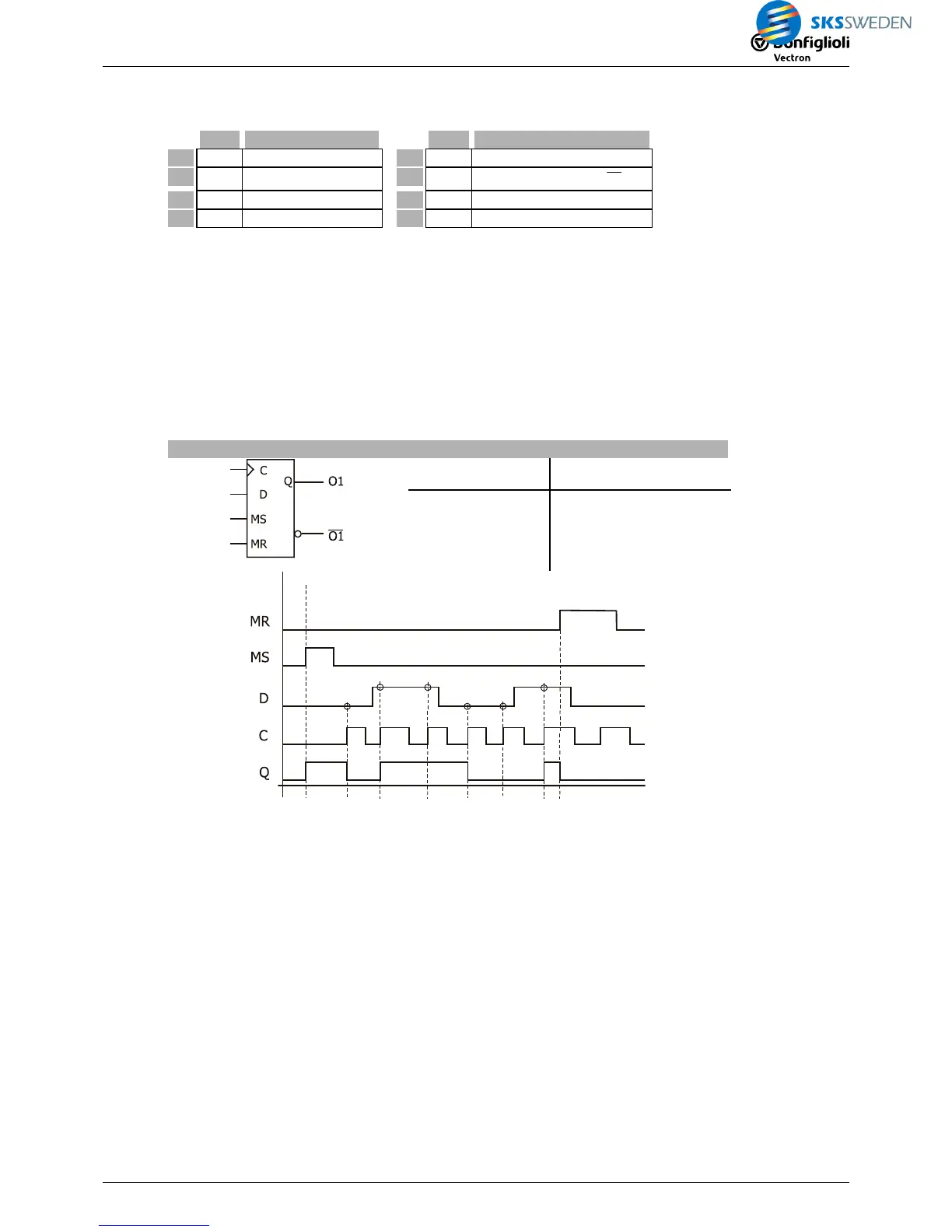

Description:

If a positive edge is received at input 1 (clock pulse input C, Clock) the signal is transferred

from signal input 2 (data input D) to the output.

TRUE at the Master Set input sets the output to TRUE. TRUE at the Master Reset input sets the

output to FALSE.

Via the output buffer, the output signal is globally available.

Master Set and Master Reset are connected parallel with the function and change the state of

the function as soon as the signal is present.

D-Flip-Flop, Master

C

D

MS

MR

O1

Q

State

x x x 1 0 Off (Master)

x x 1 0 1 On (Master)

x x 0 0 Q

n-1

Hold

0Æ1

0 0 0 0 Sample

0Æ1 1 0 0 1 Sample

Loading...

Loading...