4.1 Superior/Master

Most instructions also enable setting of selective output statuses by overriding inputs. This may

be used, for example, for initialization of a plant status.

There are two variants of instructions with overriding inputs.

Superior

− The function sequence is processed further internally in the instruction. The overriding in-

puts change the instruction output only for the time in which the overriding signal is present.

− During the set/reset phase, edges will also be detected and processed internally. If the Su-

perior Set/Superior Reset Signal is no longer present, the output will take the value which

would result without the Set/Reset Phase.

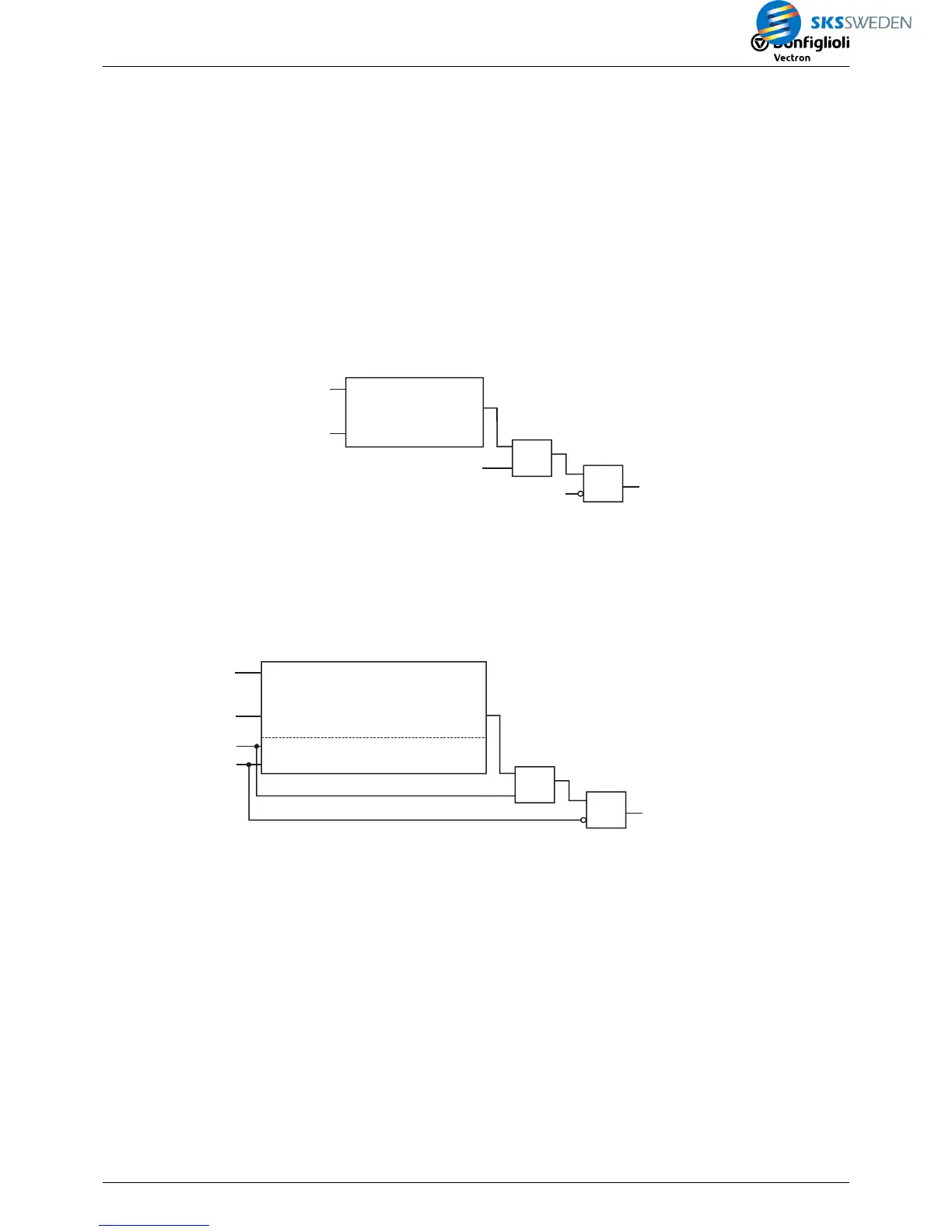

− The processing sequence can be compared to a series connection of the function and a logic

AND operation with the superior inputs.

Input 1

Input 2

Output

Superior Set

Superior Reset

&

FlipFlop

Delay

Clock generator

...

=

1

>

Master

− The function sequence is interrupted. The overriding inputs change the instruction output as

from the time at which the overriding signal is present.

− Set/Reset signals are not evaluated as long as a Master-Set/Master-Reset is present.

−

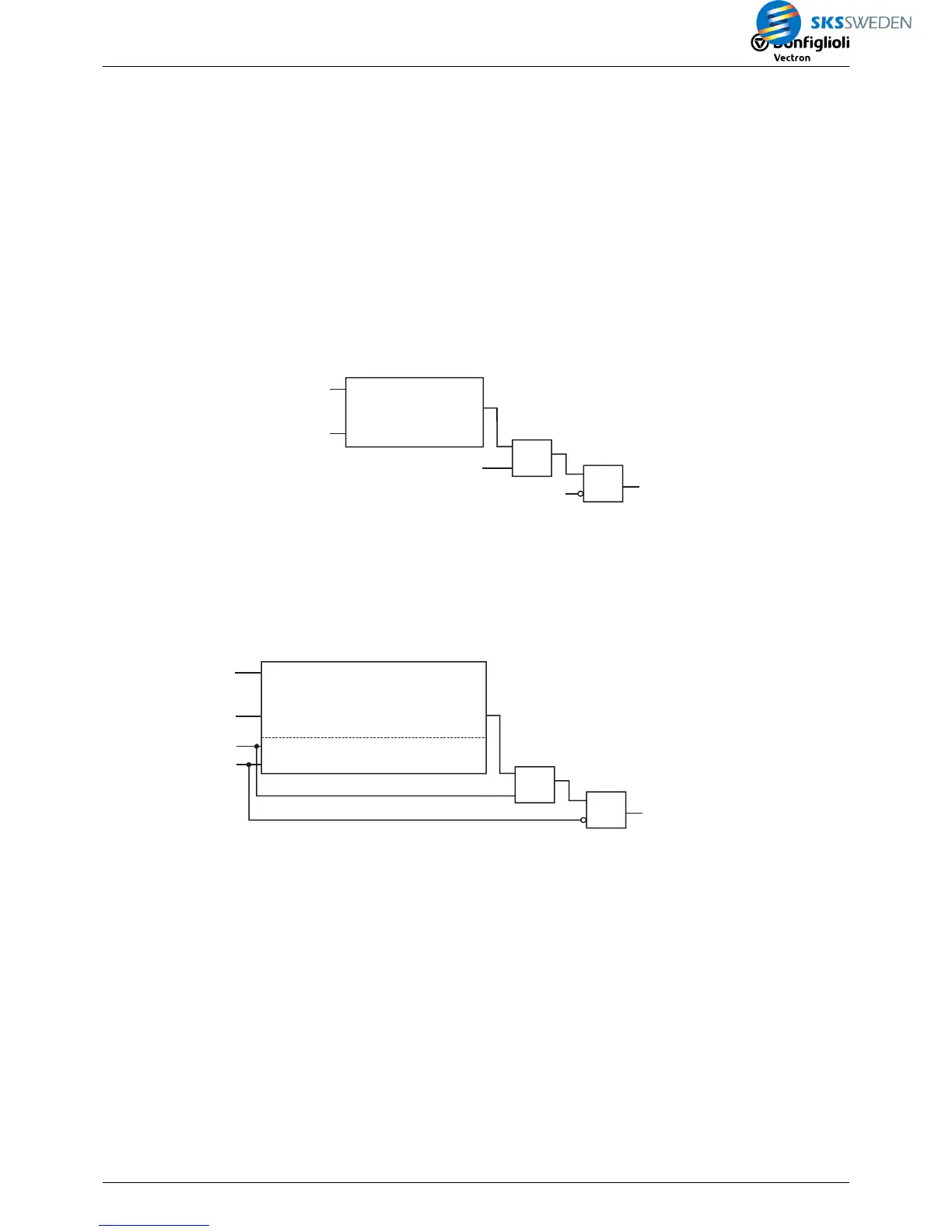

The processing sequence can be compared to a parallel connection of the function and the

master inputs.

Input 1

Input 2

Outpu

&

FlipFlop

Delay

Clock generator

...

Reset Timer

Master Set

Master Reset

=

1

>

Superior Master

Superior-Set Master-Set TRUE at Superior-Set/Master-Set switches instruction out-

put 1 to TRUE directly.

Superior Reset Master Reset TRUE at Superior-Reset/Master-Reset switches instruction

output 1 to FALSE directly. Reset has a higher priority than

set.

4.2 P1 and P2 for chronological behavior and jump target

The chronological behavior of the instructions or a jump target can be set up via P1 and P2.

Loading...

Loading...