4.6 Timer functions

4.6.1 [60,61,62] Monoflop (retriggerable), Superior

Type Function

Type Function

I1

b M, Monoflop edge 1

O1

b output O1

I2

b M¯ , Monoflop edge 2

O2

b

negated output O2 = -

1O

I3

b Superior Set input

P1

t On-time (High)

I4

b Superior Reset input

P2

t

ignore edge time

60 [ms], 61 [s] or 62 [min]

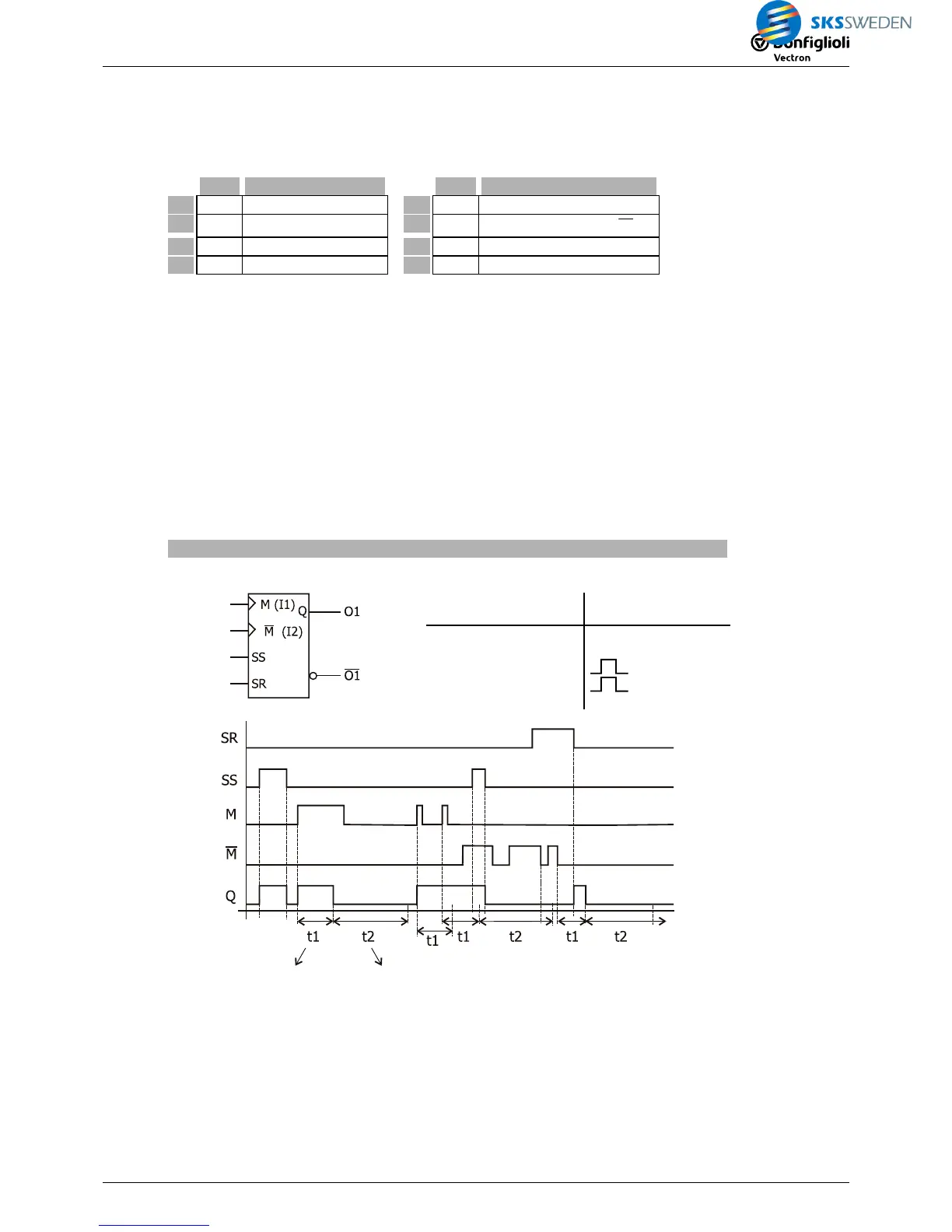

Description:

Output signal becomes TRUE with positive clock edge at input 1 or with negative clock edge at

input 2. The time set in P1 is the On-Time (High) and the time set in P2 is the ignore edge time

(Low). The set on-time starts again with each edge.

TRUE at the Superior Set input sets the output to TRUE. TRUE at the Superior Reset input sets

the output to FALSE.

Via the output buffer, the output signal is globally available.

Inputs Superior Set and Superior Reset are connected in series with the function. Levels on

Monoflop inputs I1 and I2 As soon as the Superior Set or Superior Reset is reset, the output is

switched to the internally saved value.

Monoflop (retriggerable), Superior

Digital

Input

Signal

source

Function &

output

Logic table

M

M¯

SS

SR

O1

Q

State

x x x 1 0 Off (Superior)

x x 1 0 1 On (Superior)

0Æ1 x 0 0 Pulse

x 0Æ1 0 0 Pulse

P1

(on-time)

P2

(ignore edge time)

Loading...

Loading...