2-32 Mechanism Configuration and Operating Principles Rev. A

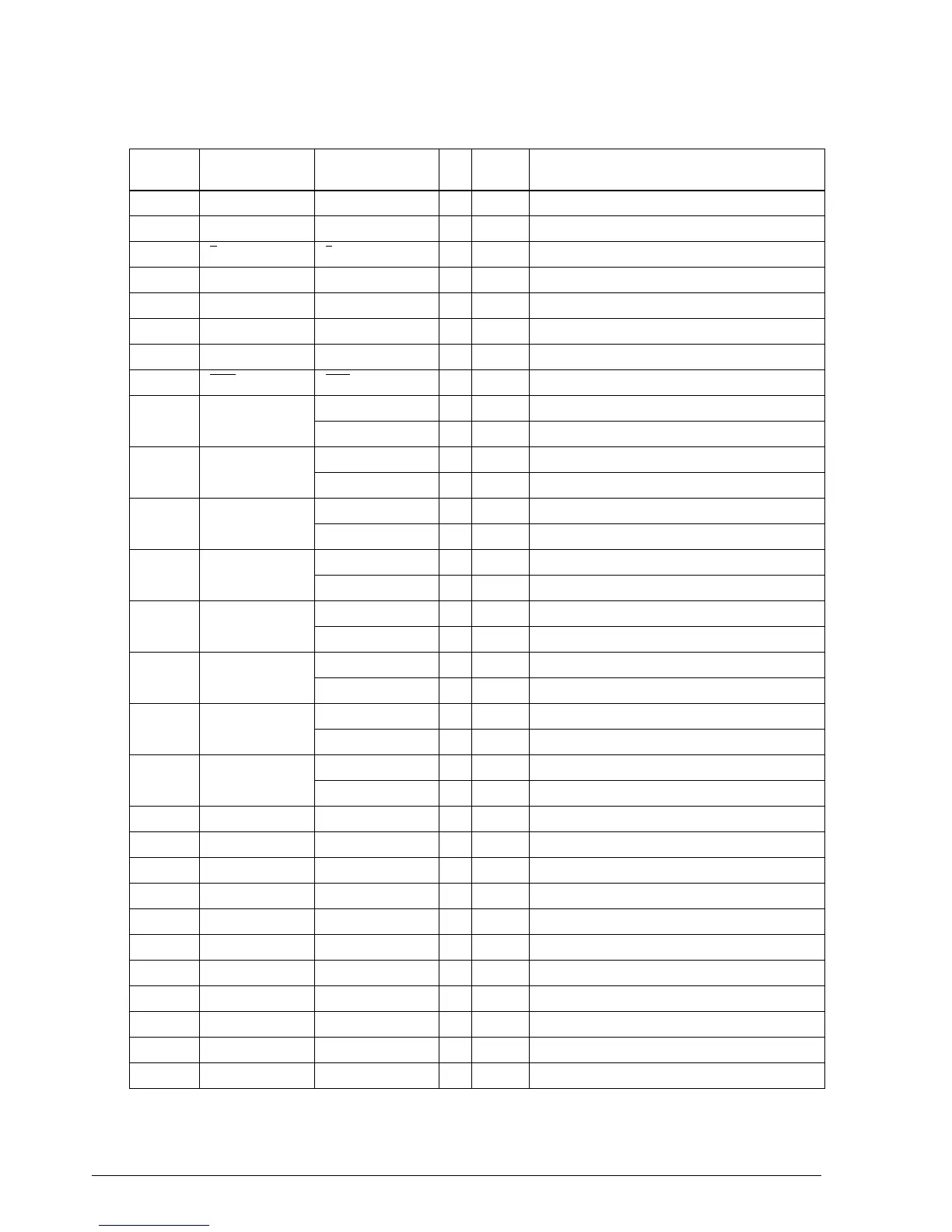

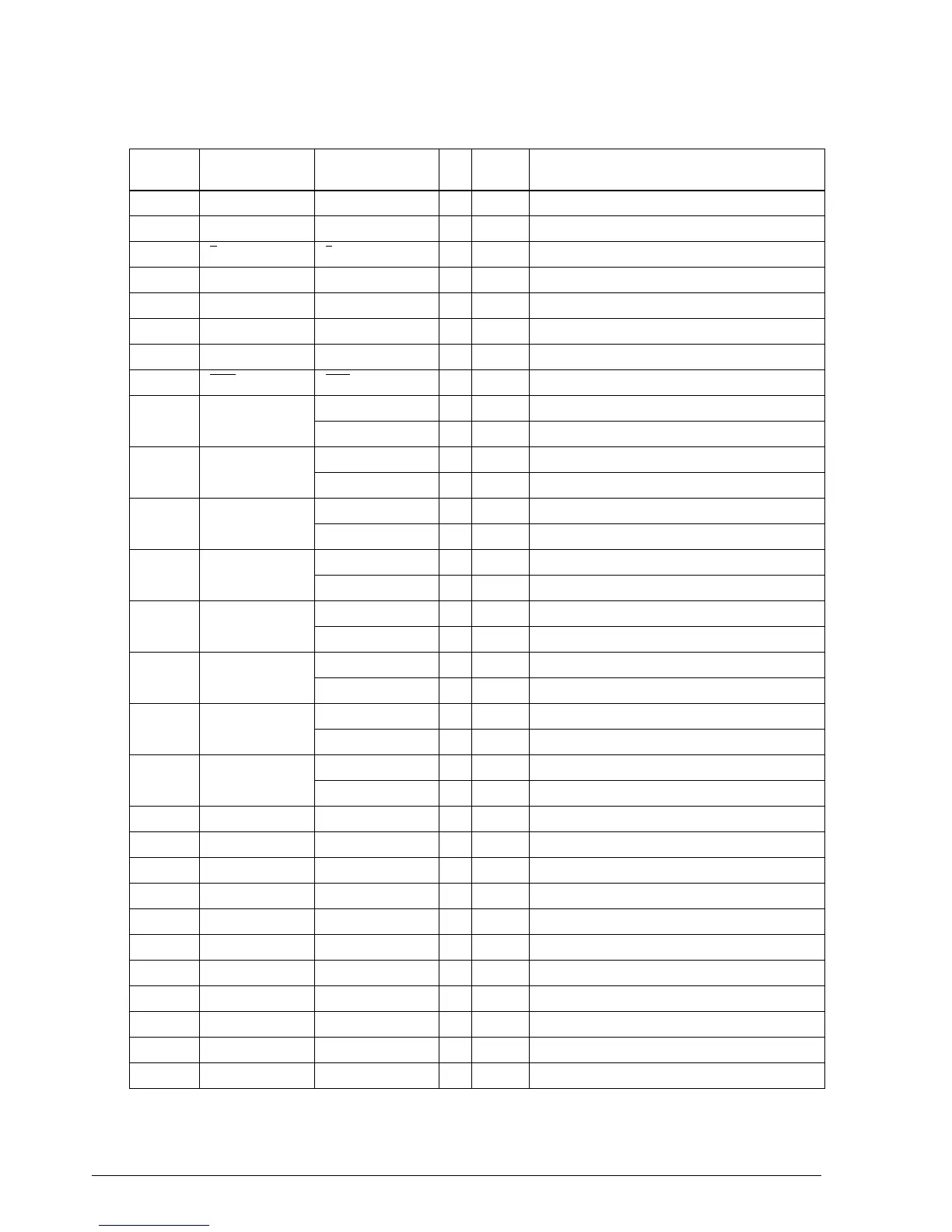

29 x

in

(x

in

) I TTL Clock input

30 X

OUT

(X

OUT

) O TTL Clock input

31 (E

)(E) O TTL Enable signal L = Data read/write)

32 (V

ss

)(V

ss

) - GND Power supply

33 HLDA HLDA O TTL Unused (open)

34 ALE ALE O TTL Address latch enable signal H = address latch

35 BHE BHE O TTL Unused (open)

36 (R/W

)(R/W) O TTL Read/write signal H = read, L = write

37 A23/D7

A23 O TTL Address signal Bit 23

D7 I/O TTL Data signal Bit 7

38 A22/D6

A22 O TTL Address signal Bit 22

D6 I/O TTL Data signal Bit 6

39 A21/D5

A21 O TTL Address signal Bit 21

D5 I/O TTL Data signal Bit 5

40 A20/D4

A20 O TTL Address signal Bit 20

D4 I/O TTL Data signal Bit 4

41 A19/D3

A19 O TTL Address signal Bit 20

D4 I/O TTL Data signal Bit 3

42 A18/D2

A18 O TTL Address signal Bit 18

D2 I/O TTL Data signal Bit 2

43 A17/D1

A17 O TTL Address signal Bit 17

D1 I/O TTL Data signal Bit 1

44 A16/D0

A16 O TTL Address signal Bit 16

D0 I/O TTL Data signal Bit 0

45 A15 A15 O TTL Address signal Bit 15

46 A14 A14 O TTL Address signal Bit 14

47 A13 A13 O TTL Address signal Bit 13

48 A12 A12 O TTL Address signal Bit 12

49 A11 A11 O TTL Address signal Bit 11

50 A10 A10 O TTL Address signal Bit 10

51 A9 A9 O TTL Address signal Bit 9

52 A8 A8 O TTL Address signal Bit 8

53 A7 A7 O TTL Address signal Bit 7

54 A6 A6 O TTL Address signal Bit 6

55 A5 A5 O TTL Address signal Bit 5

Table 2-1. CPU Pin Assignments (continued)

Pin

number

CPU function Signal designation I/O Level Description

CONFIDENTIAL

Loading...

Loading...