EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL

4-8

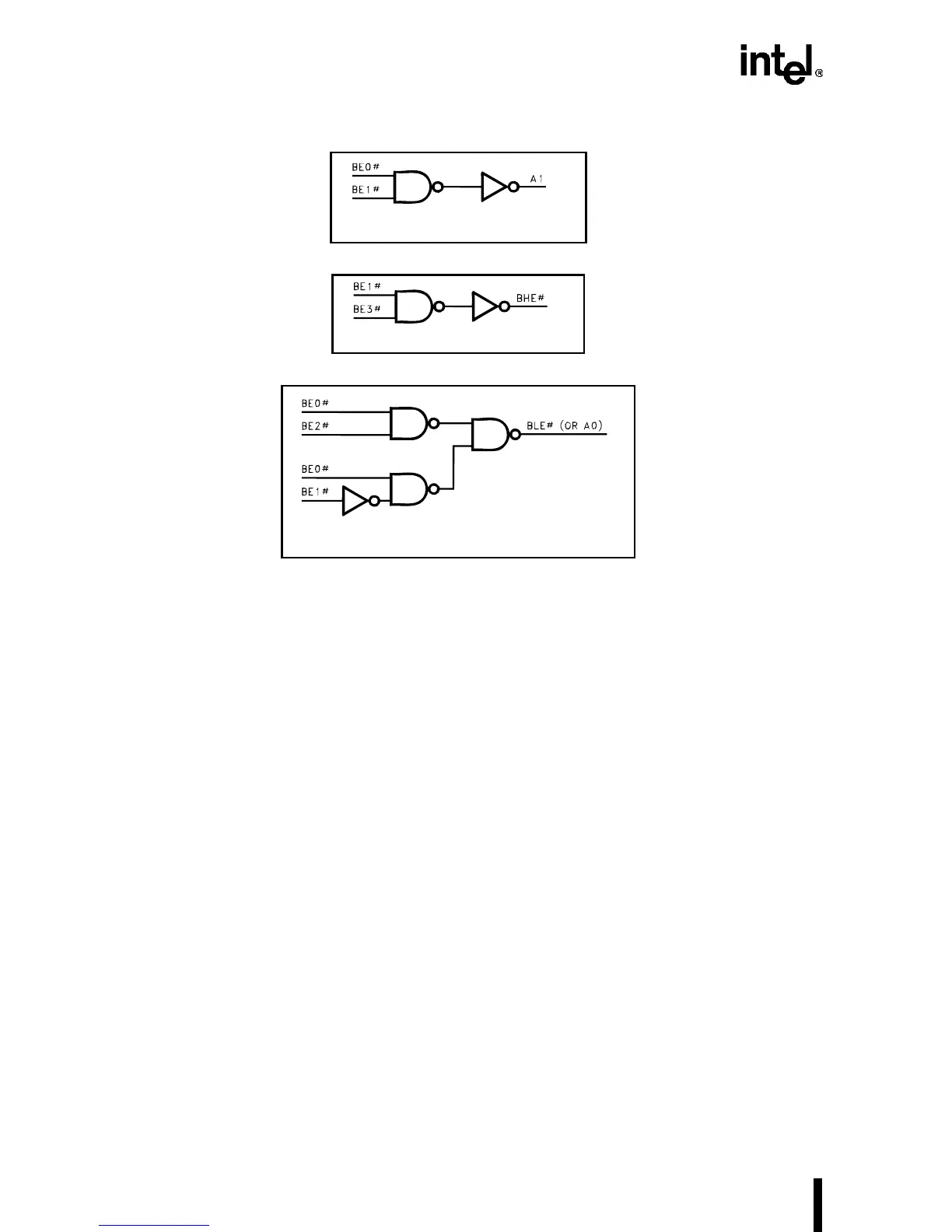

Figure 4-5. Logic to Generate A1, BHE# and BLE# for 16-Bit Buses

Combinations of BE3#–BE0# that never occur are those in which two or three asserted byte en-

ables are separated by one or more deasserted byte enables. These combinations are “don't care”

conditions in the decoder. A decoder can use the non-occurring BE3#–BE0# combinations to its

best advantage.

Figure 4-6 shows an Intel486 processor data bus interface to 16- and 8-bit wide memories. Ex-

ternal byte swapping logic is needed on the data lines so that data is supplied to and received from

the Intel486 processor on the correct data pins (see Table 4-4).

240950–42

240950–43

240950–44

Loading...

Loading...