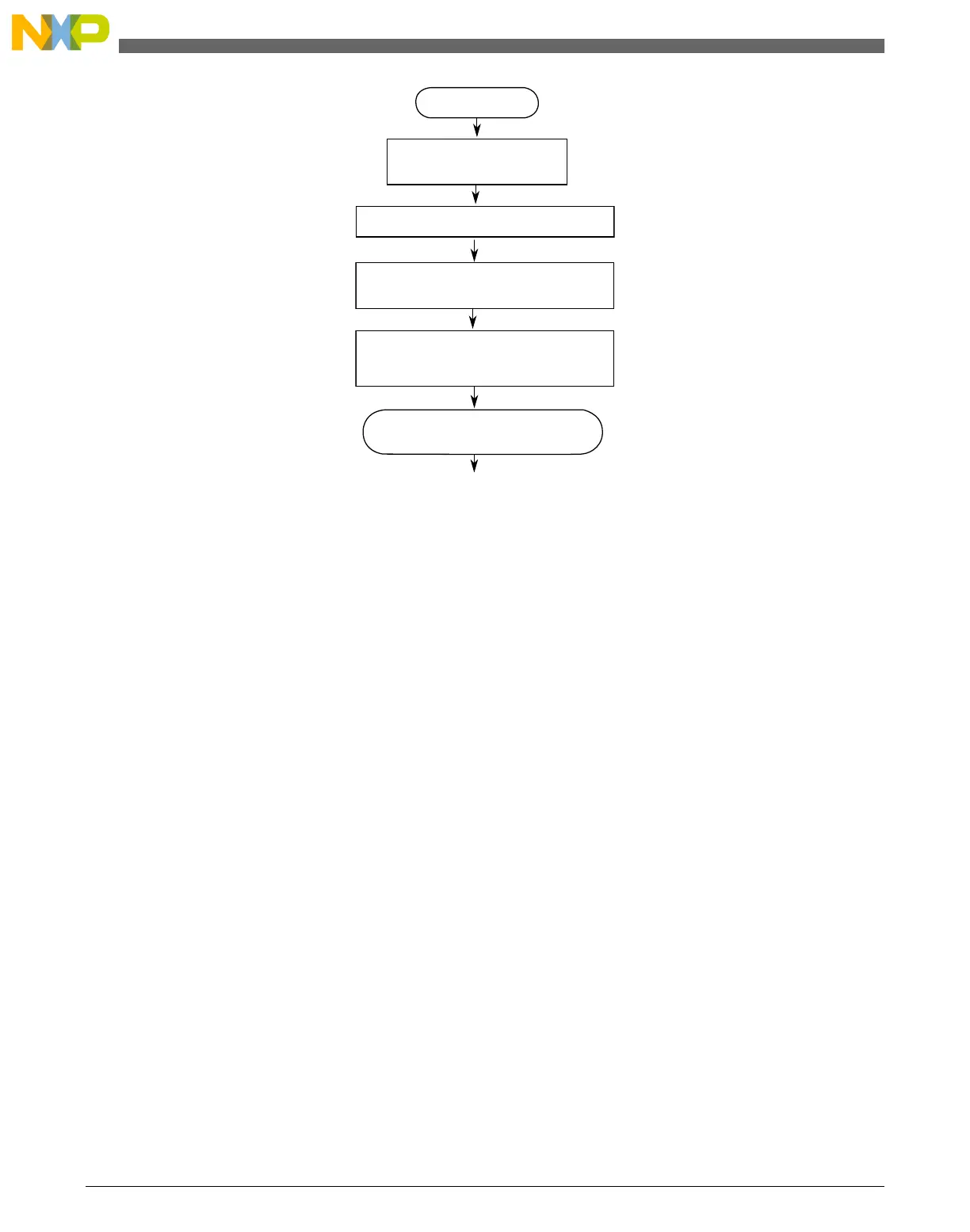

Configure SPI before Transmission

RESET

Configure DMA Controller

for SPI Transmission

Set TXDMAE/RXDMAE=1 to enable

Transmit/Receive by DMA

Set SPE=1 to start transmission in

master mode or enable SPI for

transmission in slave moe

Wait for interrupt(s) of DMA Controller

indicating end of SPI transmission

Figure 37-21. Basic Flow of SPI Transmission by DMA

37.4.4.1 Transmit by DMA

Transmit by DMA is supported only when TXDMAE is set. A transmit DMA request is

asserted when both SPE and SPTEF are set. Then the on-chip DMA controller detects

this request and transfers data from memory into the SPI data register. After that, TX

DMA DONE is asserted to clear SPTEF automatically. This process repeats until all data

for transmission (the number is decided by the configuration register[s] of the DMA

controller) is sent.

After DMA transfers the first byte to the SPI data register, the SPI pushes this data into

the shifter, thereby making SPTEF high again. This generates another DMA request

immediately, but the CPU lacks enough time to service the first DMA interrupt service

request (ISR). The subsequent DMA request is paced at the SPI transfer rate. Manage this

behavior during the first byte transfer through the DMA channel. Write the first byte to

the SPI data register via the CPU. The other bytes are transmitted by the DMA.

Functional Description

KL25 Sub-Family Reference Manual, Rev. 3, September 2012

672 Freescale Semiconductor, Inc.

Loading...

Loading...