RL78/F13, F14 CHAPTER 17 LIN/UART MODULE (RLIN3)

R01UH0368EJ0210 Rev.2.10 1126

Dec 10, 2015

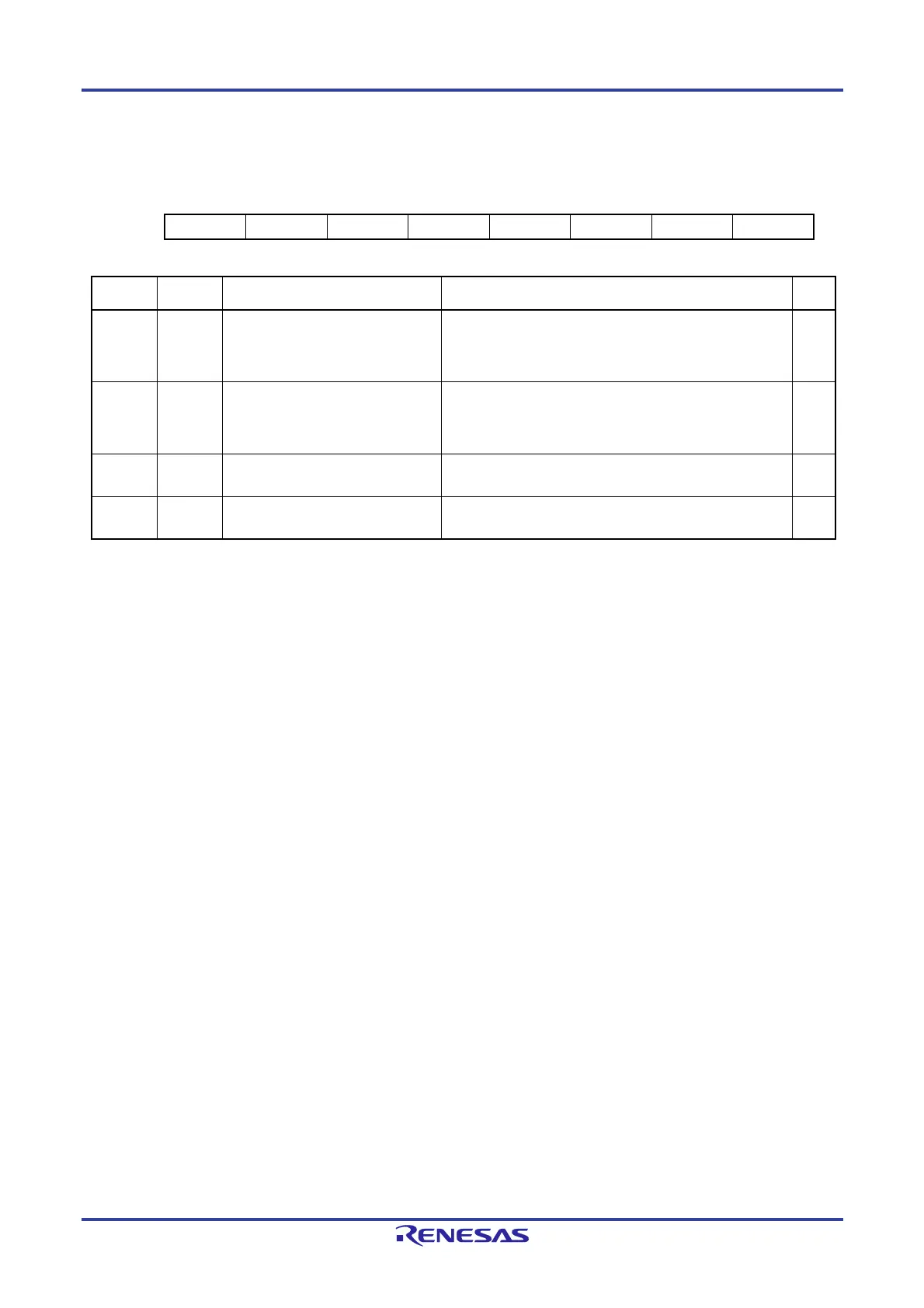

(17) LIN/UART Transmission Control Register (LTRCn)

Address: F06D0H

7 6 5 4 3 2 1 0

— — — — — —

RTS FTS

Value after reset:

0 0 0 0 0 0 0 0

Bit Symbol Bit Name Function R/W

0 FTS Frame Transmission or

Wake-up Transmission/Reception

Start

0: Frame transmission or wake-up transmission/reception is

stopped.

1: Frame transmission or wake-up transmission/reception is

started.

R/W

1 RTS Response Transmission/Reception

Start

0: Response transmission/reception is stopped in frame

separate mode.

1: Response transmission/reception is started in frame

separate mode.

R/W

2 — Reserved This bit is always read as 0. The write value should always

be 0.

R/W

7 to 3 — Reserved These bits are always read as 0. The write value should

always be 0.

R/W

FTS bit (frame transmission or wake-up transmission/reception start bit)

Set the FTS bit to 1 to start frame or wake-up transmission.

Also set this bit to 1 to allow wake-up reception (counting of the low width of the input signal).

Only 1 can be written to this bit; 0 cannot be written.

Writing a value to this bit is disabled when the OMM0 bit in the LMSTn register is 0 (LIN reset mode). This bit is set to 0

upon completion of frame or wake-up communication and transition to LIN reset mode.

RTS bit (response transmission/reception start bit)

Set the RTS bit to 1 in frame separate mode after header transmission is started (FTS bit is 1) and response transmission

data is ready. Once set, this bit is automatically cleared to 0 upon completion of frame communication or transition to LIN

reset mode.

Only 1 can be written to this bit; 0 cannot be written.

To write 1 to this bit, write 02H to the LTRCn register by using an 8-bit data transfer instruction.

Writing a value to this bit is disabled when the OMM0 bit in the LMSTn register is 0 (LIN reset mode).

Writing a value to this bit is disabled when the FTS bit is 0 (frame transmission or wake-up transmission/reception is halted).

When response data of 9 bytes or more is to be transmitted or received, set this bit to 1 each time a data group (variable

from 0 to 8 bytes) is transmitted or received. Once set, this bit is automatically cleared to 0 upon completion of data group

communication or transition to LIN reset mode.

Loading...

Loading...