RL78/F13, F14 CHAPTER 3 CPU ARCHITECTURE

R01UH0368EJ0210 Rev.2.10 182

Dec 10, 2015

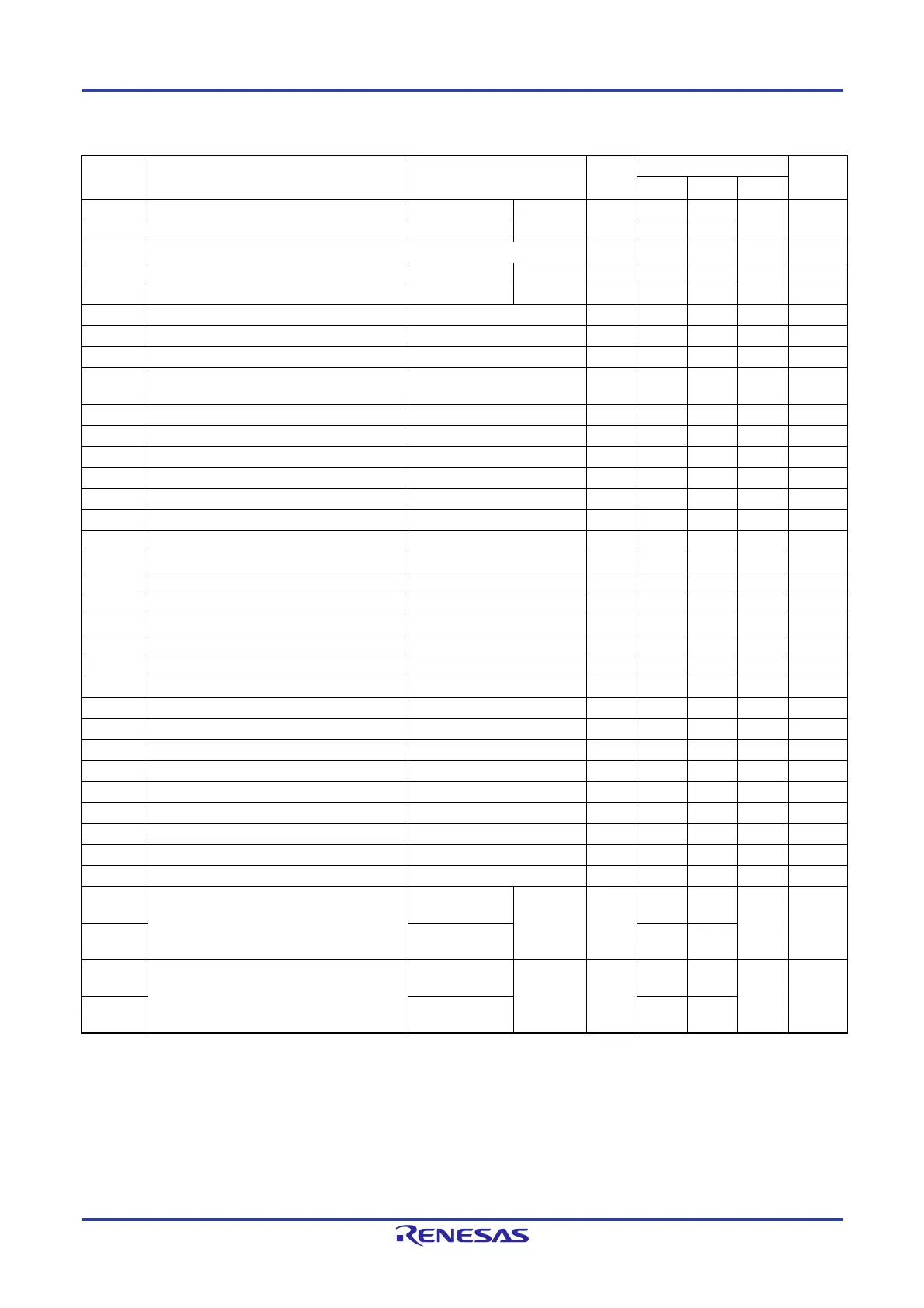

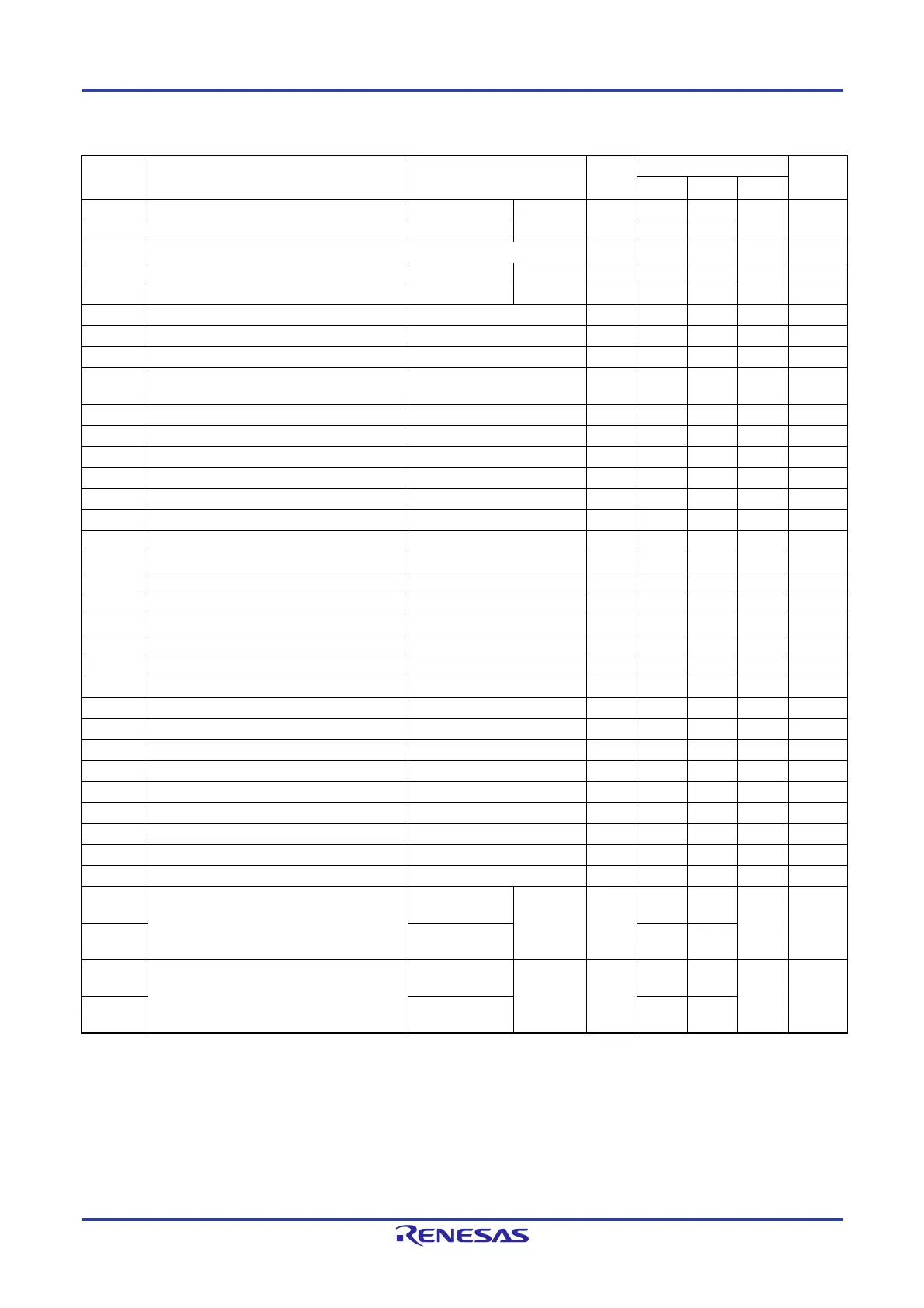

Table 3-6. Extended SFR (2nd SFR) List (31/32)

Address Special Function Register (2nd SFR) Name Symbol R/W Manipulable Bit Range After

reset

1-bit 8-bit 16-bit

F0680H CAN0 transmit history buffer access register

Note

THLACC0L THLACC0 R – √ √ 0000H

F0681H THLACC0H – √

F06C1H LIN wakeup baud rate select register LWBR0/LWBR1 R/W – √ – 00H

F06C2H LIN/UART baud rate prescaler 0 register LBRP00/LBRP10 LBRP0/

LBRP1

R/W – √ √ 00H

F06C3H LIN/UART baud rate prescaler 1 register LBRP01/LBRP11 R/W – √ 00H

F06C4H LIN self–test control register LSTC0/LSTC1 R/W – √ – 00H

F06C5H UART standby control register LUSC0/LUSC1 R/W – √ – 00H

F06C8H LIN/UART mode register LMD0/LMD1 R/W – √ – 00H

F06C9H LIN/UART break field configuration register/

UART configuration register

LBFC0/LBFC1 R/W – √ – 00H

F06CAH LIN/UART space configuration register LSC0/LSC1 R/W – √ – 00H

F06CBH LIN wakeup configuration register LWUP0/LWUP1 R/W – √ – 00H

F06CCH LIN interrupt enable register LIE0/LIE1 R/W – √ – 00H

F06CDH LIN/UART error detection enable register LEDE0/LEDE1 R/W – √ – 00H

F06CEH LIN/UART control register LCUC0/LCUC1 R/W – √ – 00H

F06D0H LIN/UART transmit control register LTRC0/LTRC1 R/W – √ – 00H

F06D1H LIN/UART mode status register LMST0/LMST1 R – √ – 00H

F06D2H LIN/UART status register LST0/LST1 R/W – √ – 00H

F06D3H LIN/UART error status register LEST0/LEST1 R/W – √ – 00H

F06D4H LIN/UART data field configuration register LDFC0/LDFC1 R/W – √ – 00H

F06D5H LIN/UART ID buffer register LIDB0/LIDB1 R/W – √ – 00H

F06D6H LIN checksum buffer register LCBR0/LCBR1 R/W – √ – 00H

F06D7H UART data buffer 0 register LUDB00/LUDB10 R/W – √ – 00H

F06D8H LIN/UART data buffer 1 register LDB01/LDB11 R/W – √ – 00H

F06D9H LIN/UART data buffer 2 register LDB02/LDB12 R/W – √ – 00H

F06DAH LIN/UART data buffer 3 register LDB03/LDB13 R/W – √ – 00H

F06DBH LIN/UART data buffer 4 register LDB04/LDB14 R/W – √ – 00H

F06DCH LIN/UART data buffer 5 register LDB05/LDB15 R/W – √ – 00H

F06DDH LIN/UART data buffer 6 register LDB06/LDB16 R/W – √ – 00H

F06DEH LIN/UART data buffer 7 register LDB07/LDB17 R/W – √ – 00H

F06DFH LIN/UART data buffer 8 register LDB08/LDB18 R/W – √ – 00H

F06E0H UART operation enable register LUOER0/LUOER1 R/W – √ – 00H

F06E1H UART option register 1 LUOR01/LUOR11 R/W – √ – 00H

F06E4H UART transmit data register LUTDR0L/

LUTDR1L

LUTDR0/

LUTDR1

R/W – √ √ 0000H

F06E5H LUTDR0H/

LUTDR1H

– √

F06E6H UART receive data register LURDR0L/

LURDR1L

LURDR0/

LURDR1

R – √ √ 0000H

F06E7H LURDR0H/

LURDR1H

– √

Note These registers are allocated to the RAM window 1 for the CAN module (receive buffer, receive FIFO buffer,

transmit/receive FIFO buffer, transmit buffer, and transmit history data). When setting these registers, set the

RPAGE bit in the GRWCR register to 1.

Loading...

Loading...