RL78/F13, F14 CHAPTER 12 A/D CONVERTER

R01UH0368EJ0210 Rev.2.10 711

Dec 10, 2015

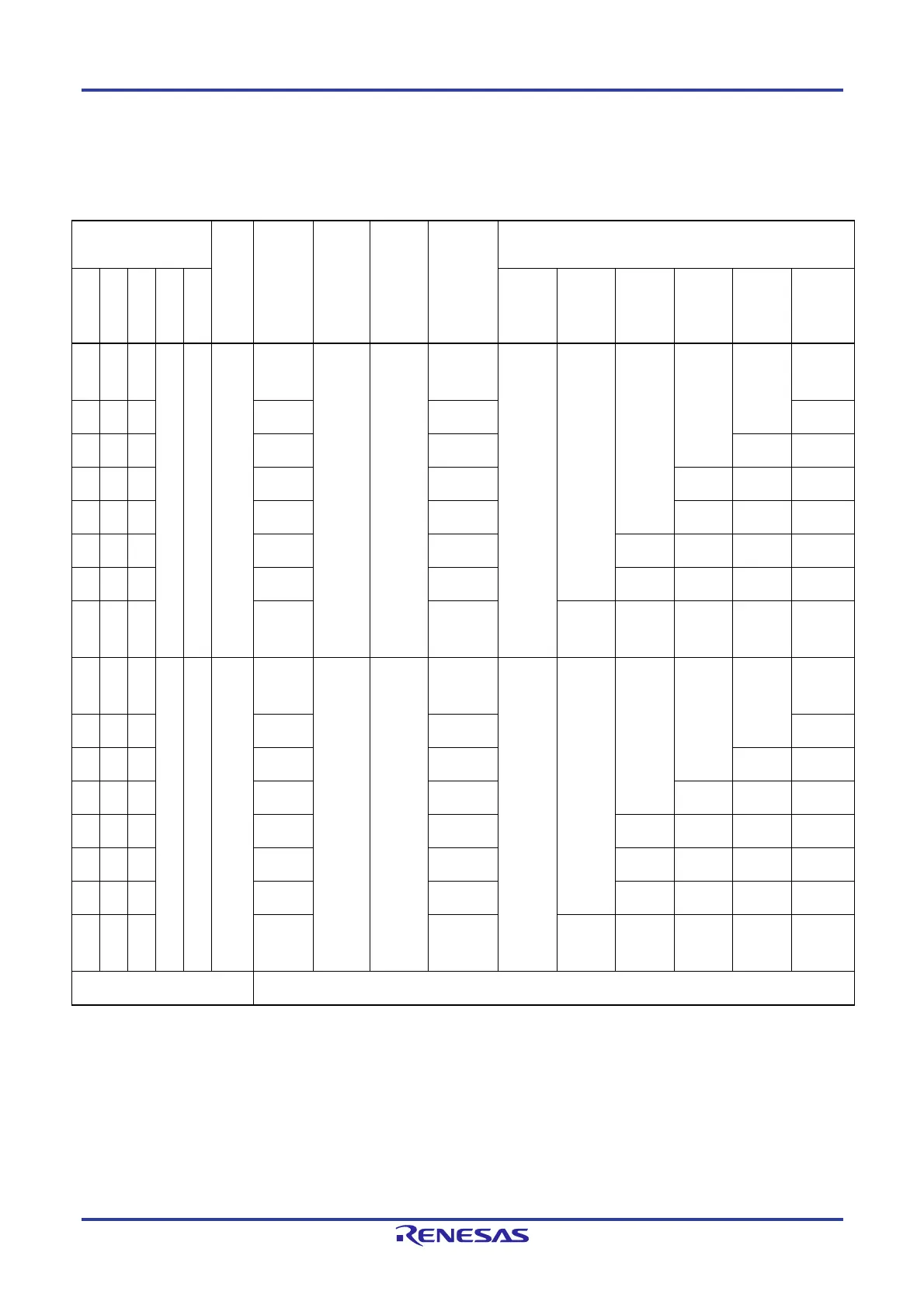

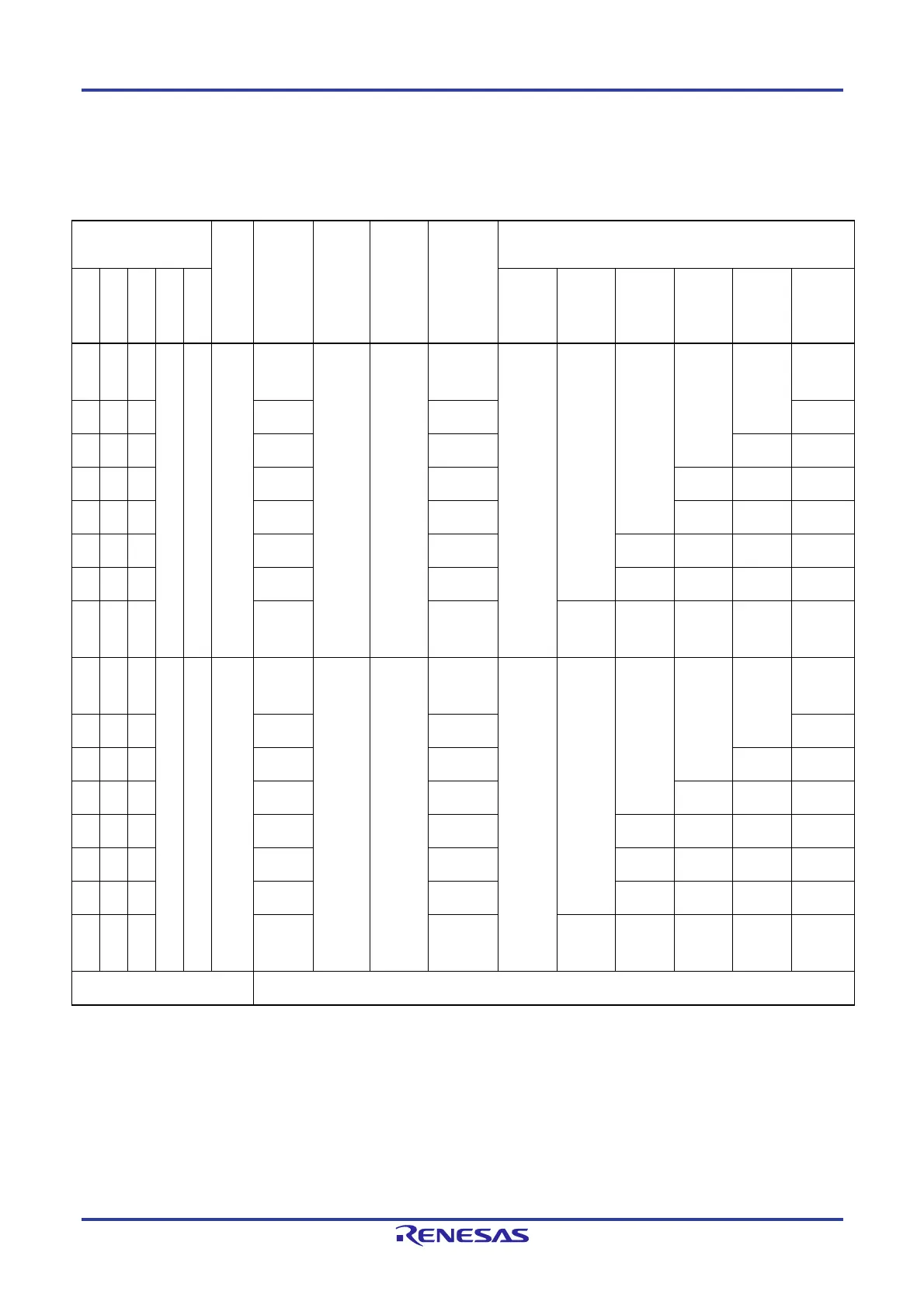

Table 12-3. A/D Conversion Time Selection (1/4)

(1) 4.0 V V

DD 5.5 V

When there is stabilization wait time (hardware trigger wait mode)

A/D Converter Mode

Register 0 (ADM0)

Mode Conversion

Clock

(f

AD)

Number of

A/D Power

Supply

Stabilization

Wait Clocks

Number

of

conversion

clocks

A/D Power

Supply

Stabilization

Wait Time +

Conversion

Time

Conversion Time Selection

FR2 FR1 FR0 LV1 LV0 fCLK =

1 MHz

fCLK =

2 MHz

fCLK =

4 MHz

fCLK =

8 MHz

fCLK =

16 MHz

fCLK =

32 MHz

0 0 0 0 0 Normal

1

fCLK/64 8 fAD 19 fAD

(number of

sampling

clocks:

7 f

AD)

1728/f

CLK Setting

prohibited

Setting

prohibited

Setting

prohibited

Setting

prohibited

Setting

prohibited

Setting

prohibited

0 0 1 fCLK/32 864/fCLK 27 s

0 1 0 fCLK/16 432/fCLK 27 s 13.5 s

0 1 1 fCLK/8 216/fCLK 27 s 13.5 s 6.75 s

1 0 0 fCLK/6 162/fCLK 20.25 s 10.125 s 5.0625 s

1 0 1 fCLK/5 135/fCLK 33.75 s 16.875 s 8.4375 s 4.21875 s

1 1 0 fCLK/4 108/fCLK 27 s 13.5 s 6.75 s 3.375 s

1 1 1 fCLK/2 54/fCLK 27 s 13.5 s 6.75 s 3.375 s Setting

prohibited

0 0 0 0 1 Normal

2

fCLK/64 8 fAD 17 fAD

(number of

sampling

clocks:

5 f

AD)

1600/f

CLK Setting

prohibited

Setting

prohibited

Setting

prohibited

Setting

prohibited

Setting

prohibited

Setting

prohibited

0 0 1 fCLK/32 800/fCLK 25 s

0 1 0 fCLK/16 400/fCLK 25 s 12.5 s

0 1 1 fCLK/8 200/fCLK 25 s 12.5 s 6.25 s

1 0 0 fCLK/6 150/fCLK 37.5 s 18.75 s 9.375 s 4.6875 s

1 0 1 fCLK/5 125/fCLK 31.25 s 15.625 s 7.8125 s 3.90625 s

1 1 0 fCLK/4 100/fCLK 25 s 12.5 s 6.25 s 3.125 s

1 1 1 fCLK/2 50/fCLK 25 s 12.5 s 6.25 s 3.125 s Setting

prohibited

Other than above Setting prohibited

Cautions 1. When rewriting the FR2 to FR0, LV1, and LV0 bits to other than the same data, stop A/D conversion

once (ADCS = 0) beforehand.

2. The above conversion time does not include clock frequency errors. Select conversion time, taking

clock frequency errors into consideration.

3. In the hardware trigger wait mode, the conversion time includes the time spent waiting for stabilization

after the hardware trigger is detected.

4. These are the numbers of clock cycles when conversion is with 10-bit resolution. When eight-bit

resolution is selected, the values are shorter by two cycles of the conversion clock (f

AD).

Remark f

CLK: CPU/peripheral hardware clock frequency

Loading...

Loading...