www.ti.com

Registers

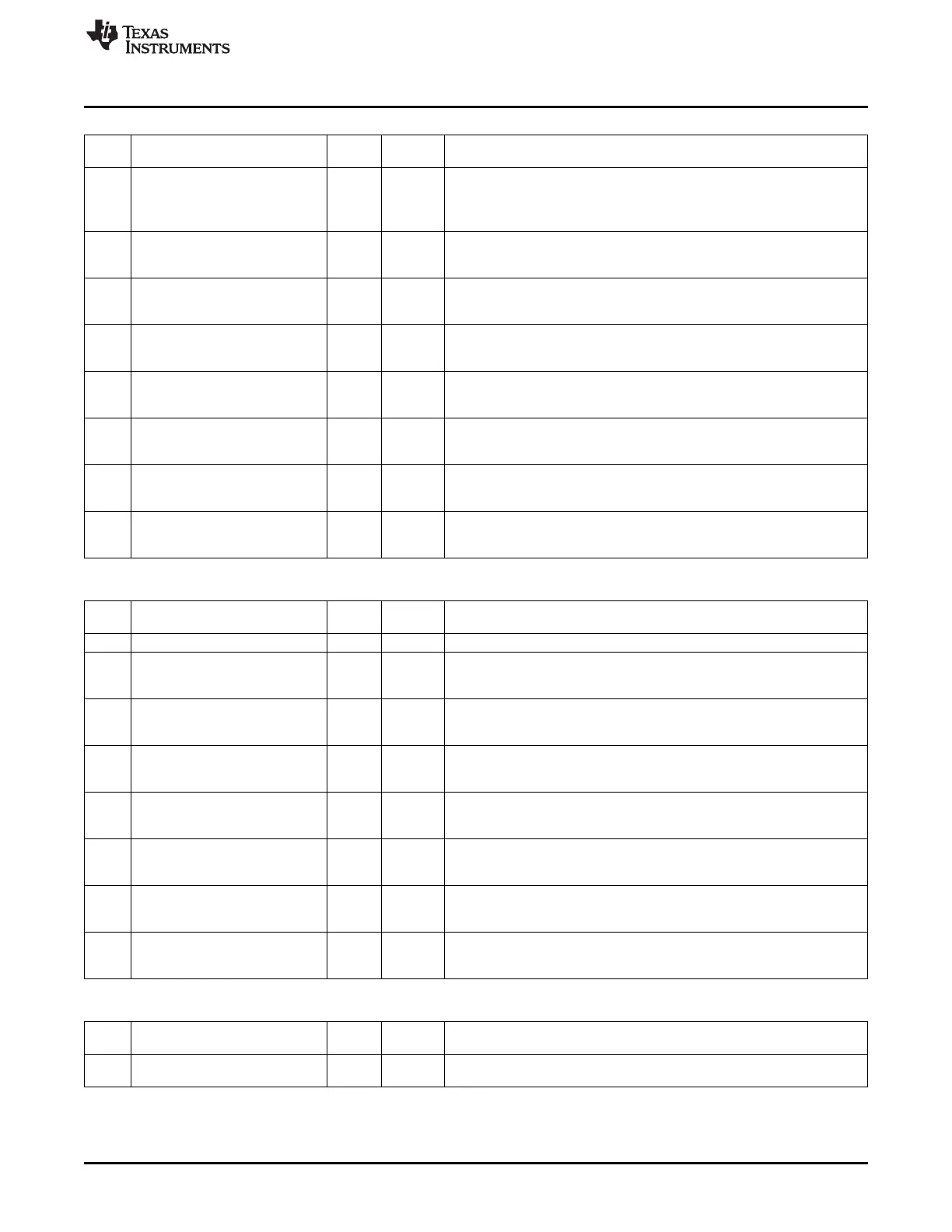

RFIRQF1 (0x91) – RF Interrupt Flags

Bit

Name Reset R/W Description

No.

7

PINGRSP

0 R/W0 When receiving a CMD_PING command, the LLE responds with a

PINGRSP. This can be used for checking that the LLE is running.

0: No interrupt pending

1: Interrupt pending

6

TASKDONE

0 R/W0 Task ended

0: No interrupt pending

1: Interrupt pending

5

TXDONE

0 R/W0 Packet transmitted

0: No interrupt pending

1: Interrupt pending

4

RXEMPTY

0 R/W0 Empty packet received

0: No interrupt pending

1: Interrupt pending

3

RXIGNORED

0 R/W0 Packet received with unexpected sequence number

0: No interrupt pending

1: Interrupt pending

2

RXNOK

0 R/W0 Packet received with CRC error

0: No interrupt pending

1: Interrupt pending

1

TXFLUSHED

0 R/W0 Tx ACK buffer flushed

0: No interrupt pending

1: Interrupt pending

0

RXOK

0 R/W0 Packet received correctly

0: No interrupt pending

1: Interrupt pending

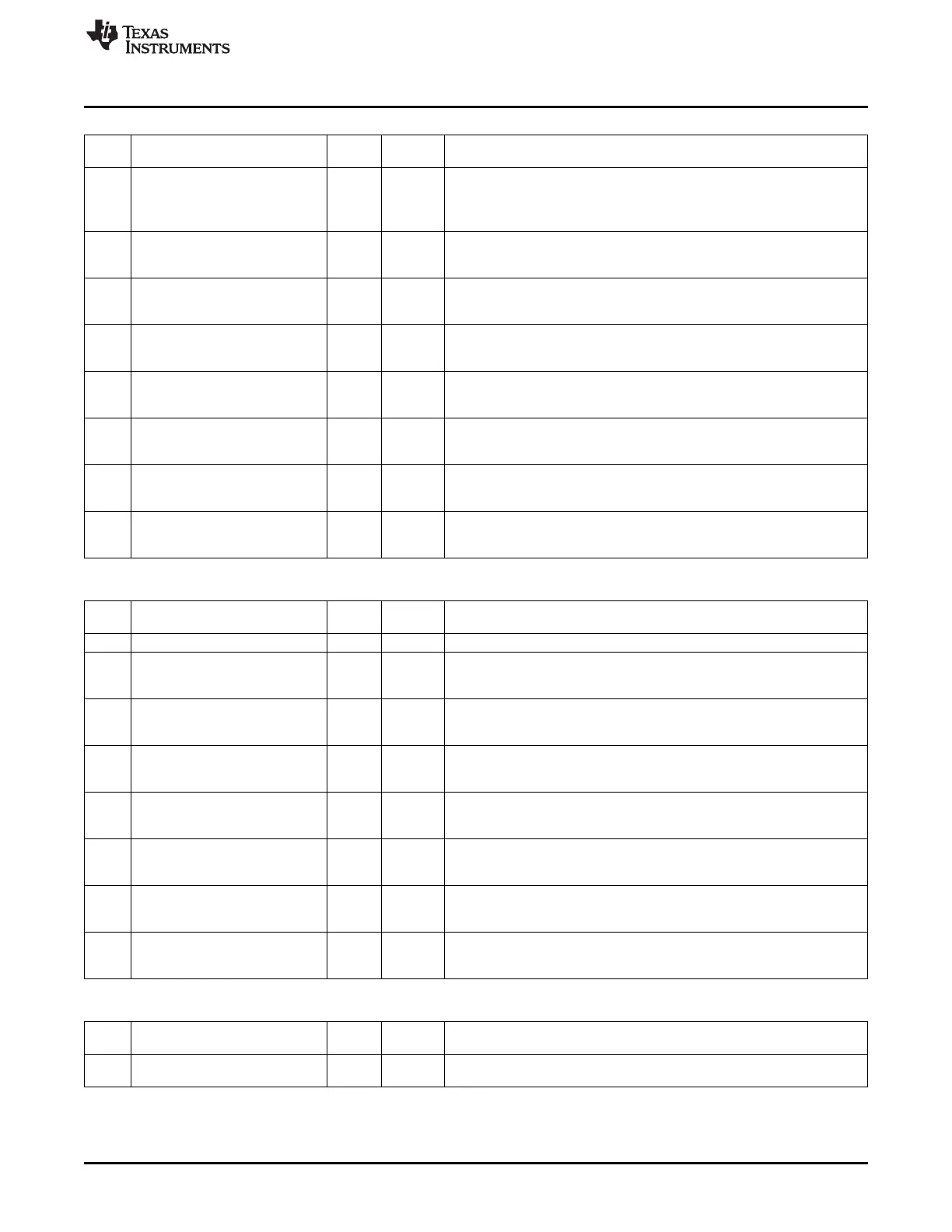

RFERRF (0xBF) – RF Error Interrupt Flags

Bit

Name Reset R/W Description

No.

7 – 0 R/W0 Reserved

6

RXFIFOFULL

0 R/W0 Rx FIFO is full when trying to store received data

0: No interrupt pending

1: Interrupt pending

5

LLEERR

0 R/W0 LLE command or parameter error

0: No interrupt pending

1: Interrupt pending

4

RXTXABO

0 R/W0 Receive or transmit operation aborted

0: No interrupt pending

1: Interrupt pending

3

RXOVERF

0 R/W0 Rx FIFO overflow

0: No interrupt pending

1: Interrupt pending

2

TXOVERF

0 R/W0 Tx FIFO overflow

0: No interrupt pending

1: Interrupt pending

1

RXUNDERF

0 R/W0 Rx FIFO underflow

0: No interrupt pending

1: Interrupt pending

0

TXUNDERF

0 R/W0 Tx FIFO underflow

0: No interrupt pending

1: Interrupt pending

RFD (0xD9) – RF data

Bit

Name Reset R/W Description

No.

7:0 0x00 R/W Data written to the register is written to the Tx FIFO. When reading this

RFD[7:0]

register, data from the Rx FIFO is read.

335

SWRU191C–April 2009–Revised January 2012 CC2541 Proprietary Mode Radio

Submit Documentation Feedback

Copyright © 2009–2012, Texas Instruments Incorporated

Loading...

Loading...