STATus:OPERation:CONDition?

Returns the sum of the bits in the condition register for the Standard Operation Register group. This register is read-

only; bits are not cleared when read.

A condition register continuously monitors the state of the instrument. Condition register bits are updated in real time;

they are neither latched nor buffered.

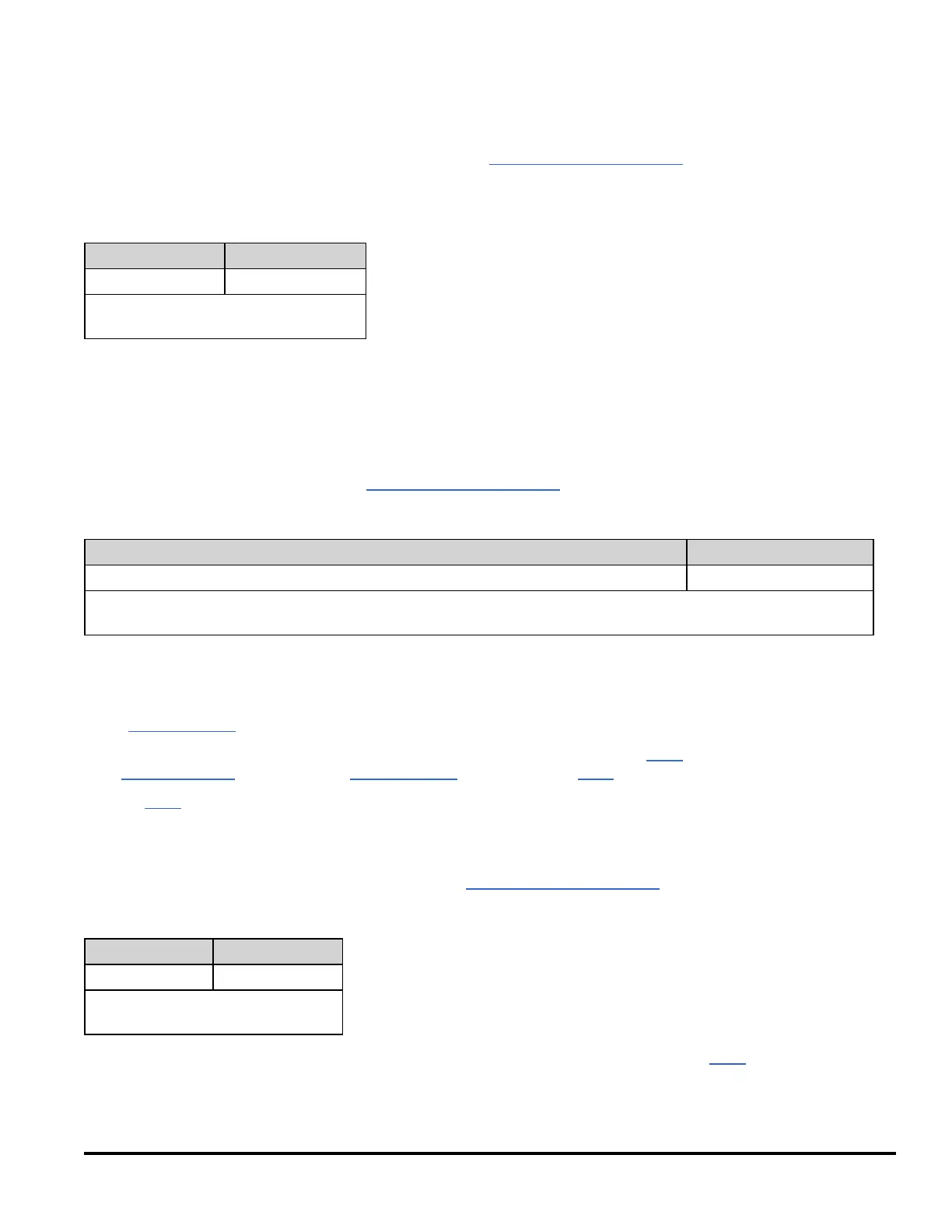

Parameter Typical Return

(none) +32

Read the condition register (bit 5 is set):

STAT:OPER:COND?

l The condition register bits reflect the current condition. If a condition goes away, the corresponding bit is cleared in

the condition register.

STATus:OPERation:ENABle <enable_value>

STATus:OPERation:ENABle?

Enables bits in the enable register for the Standard Operation Register group. The selected bits are then reported to the

Status Byte. An enable register defines which bits in the event register will be reported to the Status Byte register

group. You can write to or read from an enable register.

Parameter Typical Return

A decimal value that corresponds to the binary-weighted sum of the bits in the register. +32

Enable bit 5 (decimal value 32) in the enable register.

STAT:OPER:ENAB 32

l Use the <enable> parameter to specify which bits will be reported to the Status Byte. The decimal value specified

corresponds to the binary-weighted sum of the bits you wish to enable in the register. For example, to enable bit 5

(decimal value = 32) and bit 9 (decimal value = 512), the corresponding decimal value would be 544 (32 + 512).

l A STATus:PRESet clears all bits in the enable register.

l The <enable> setting is nonvolatile; it does not change after a Factory Reset (*RST) , Instrument Preset

(SYSTem:PRESet), Status Preset (STATus:PRESet) or Clear Status (*CLS).

l The *PSC command controls whether the enable register is cleared at power on.

STATus:OPERation[:EVENt]?

Returns the sum of the bits in the event register for the Standard Operation Register group. An event register is a read-

only register that latches events from the condition register. While an event bit is set, subsequent events

corresponding to that bit are ignored. The register bits are cleared when you read the register.

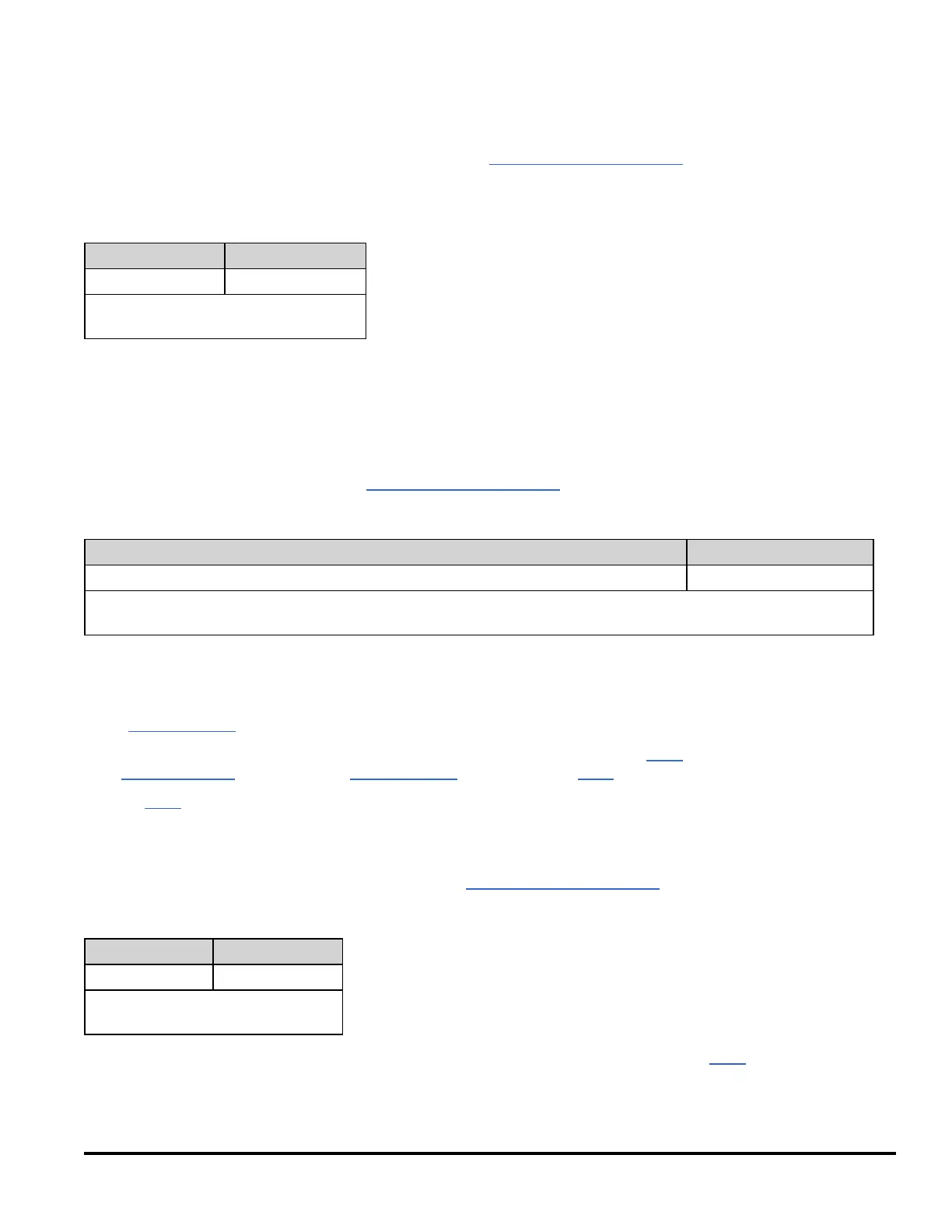

Parameter Typical Return

(none) +512

Read the event register (bit 9 is set):

STAT:OPER:EVEN?

l Once a bit is set, it remains set until cleared by reading the event register or by sending *CLS (clear status).

Agilent Truevolt Series DMM Operating and Service Guide 227

Loading...

Loading...