Titanium Interfaces User Guide

Using the MIPI TX Lane or MIPI RX Lane Block

The following tables show how to implement a MIPI TX Lane or MIPI RX Lane block.

Later sections explain how to build a complete interface.

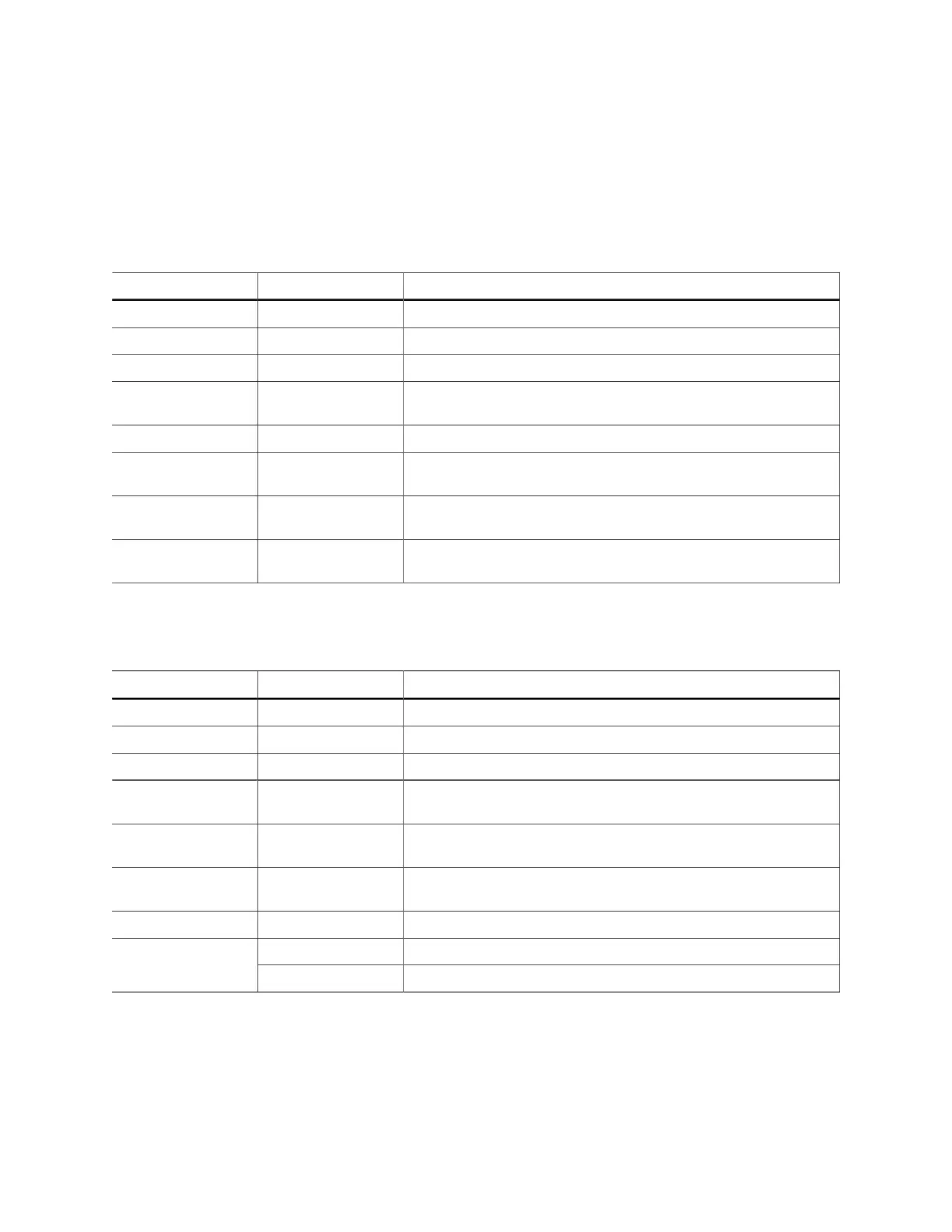

MIPI TX Lane Block

Table 53: MIPI TX Lane Block

Option Choices Description

Instance Name User defined Type the instance name and press enter.

MIPI Lane Resource Resource list Choose a resource

Mode data lane, clock lane Choose whether the block is a clock lane or data lane.

Enable LP Reverse

Communication

On or off When on, specify the low-power N and P pins.

Pin names (various) User defined Specify the interface bus and pin names.

Serial Clock Pin

Name

User defined Name you are using for FASTCLK_D or FASTCLK_C.

Parallel Clock Pin

Name

User defined Name you are using for SLOWCLK.

Static Delay Mode

Setting

0 - 63 Choose the amount of static delay, each step adds approximately

25 ps of delay.

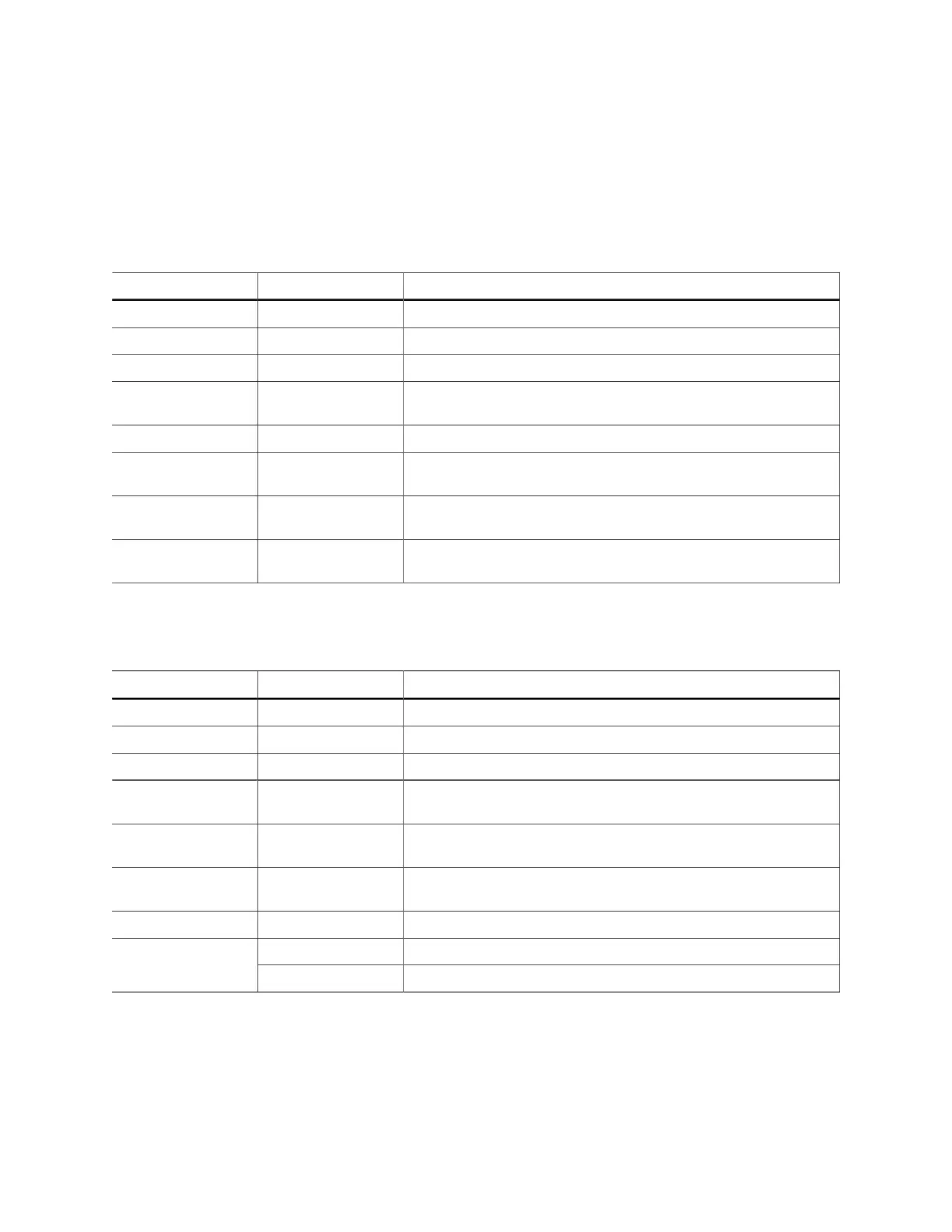

MIPI RX Lane Block

Table 54: MIPI RX Lane Block

Option Choices Description

Instance Name User defined Type the instance name and press enter.

MIPI Lane Resource Resource list Choose a resource.

Mode data lane, clock lane Choose whether the block is a clock lane or data lane.

Connection Type gclk, rclk In clock lane mode, choose global clock (gclk) or regional clock

(rclk).

Enable LP Reverse

Communication

On or off When on, specify the low-power N and P pins.

Enable Clock

Crossing FIFO

On or off When on, specify the FIFO read and empty pins.

Pin names (various) User defined Specify the interface bus and pin names.

static Integer from 0 - 63. Each step adds approximately 25 ps of delay.Delay Mode

dynamic Specify the pin names to control the dynamic delay.

www.efinixinc.com 103

Loading...

Loading...