Titanium Interfaces User Guide

LVDS Bidirectional

The LVDS bidirectional block has the same options and choices as the LVDS RX and TX

blocks.

Important: You must use the same value for the serialization/deserialization.

PLL Requirements for Serial and Parallel Clocks

With Titanium FPGAs, you need to use the output clocks from specific PLLs as the LVDS

serial and parallel clocks.

Table 44: PLL Requirements

FPGA Side PLL

Left BL_PLL, TL_PLL

Right BR_PLL, TR_PLL

Top TR_PLL, TL_PLL

Ti35, Ti60, Ti60ES

Bottom BR_PLL, BL_PLL

Create an LVDS TX Interface

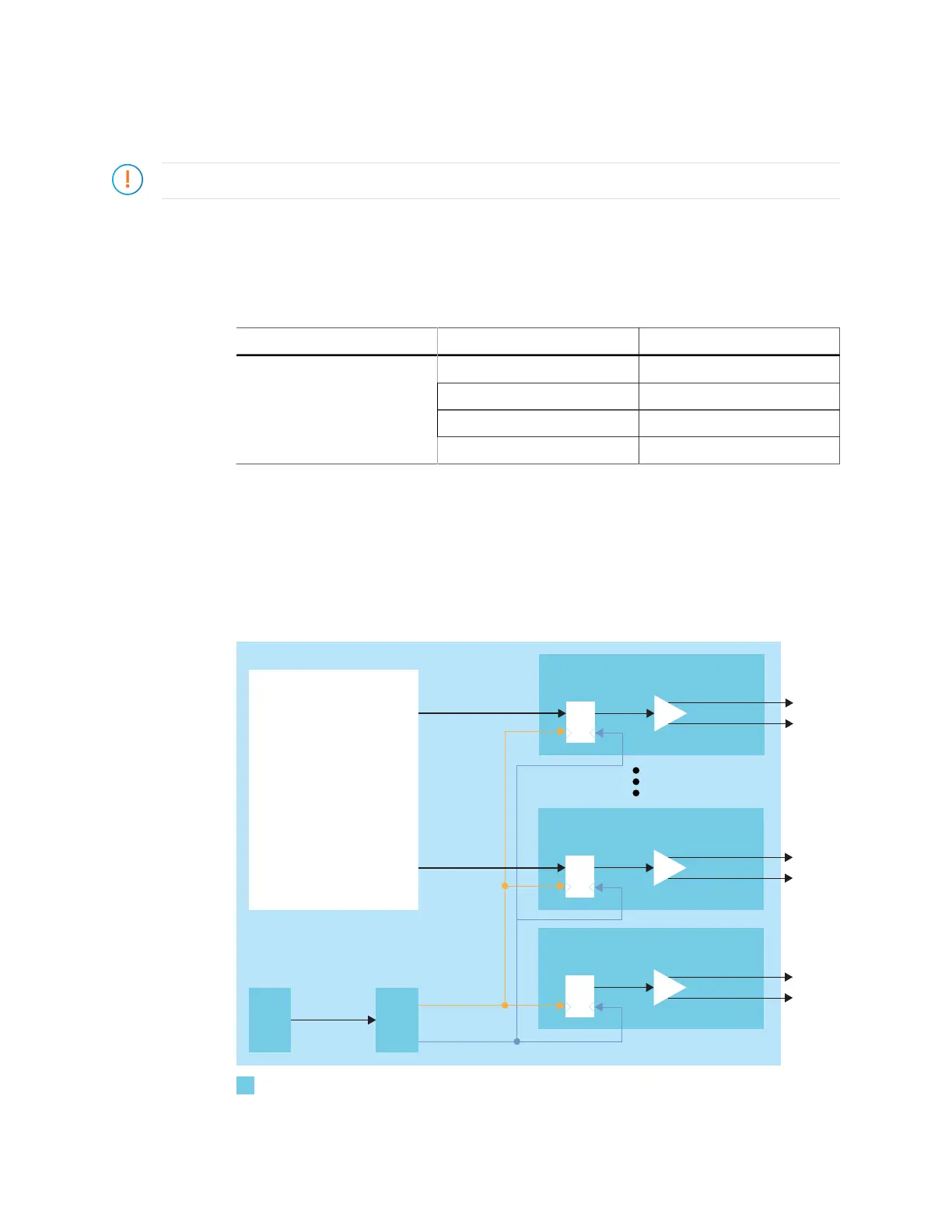

The following figure shows a completed LVDS TX interface, where n is the serialization

width and m is the number of TX lanes.

Figure 27: Complete LVDS TX Interface Block Diagram

Serializer

TXP

TXN

PLL

SLOWCLK

FASTCLK

Transmitter

LVDS TX Reference Clock Output

Serializer

TXP

TXN

OUT[n:0]

Transmitter

LVDS TXm

GPIO

PLL_CLKIN

m is the number

Follow these steps to build an LVDS TX interface using the Efinity

®

Interface Designer.

www.efinixinc.com 75

Loading...

Loading...