Titanium Interfaces User Guide

Using the LVDS Block

The LVDS block defines the functionality of the LVDS pins. You can choose whether the

block is a transmitter (TX), receiver (RX), or bidirectional.

LVDS TX

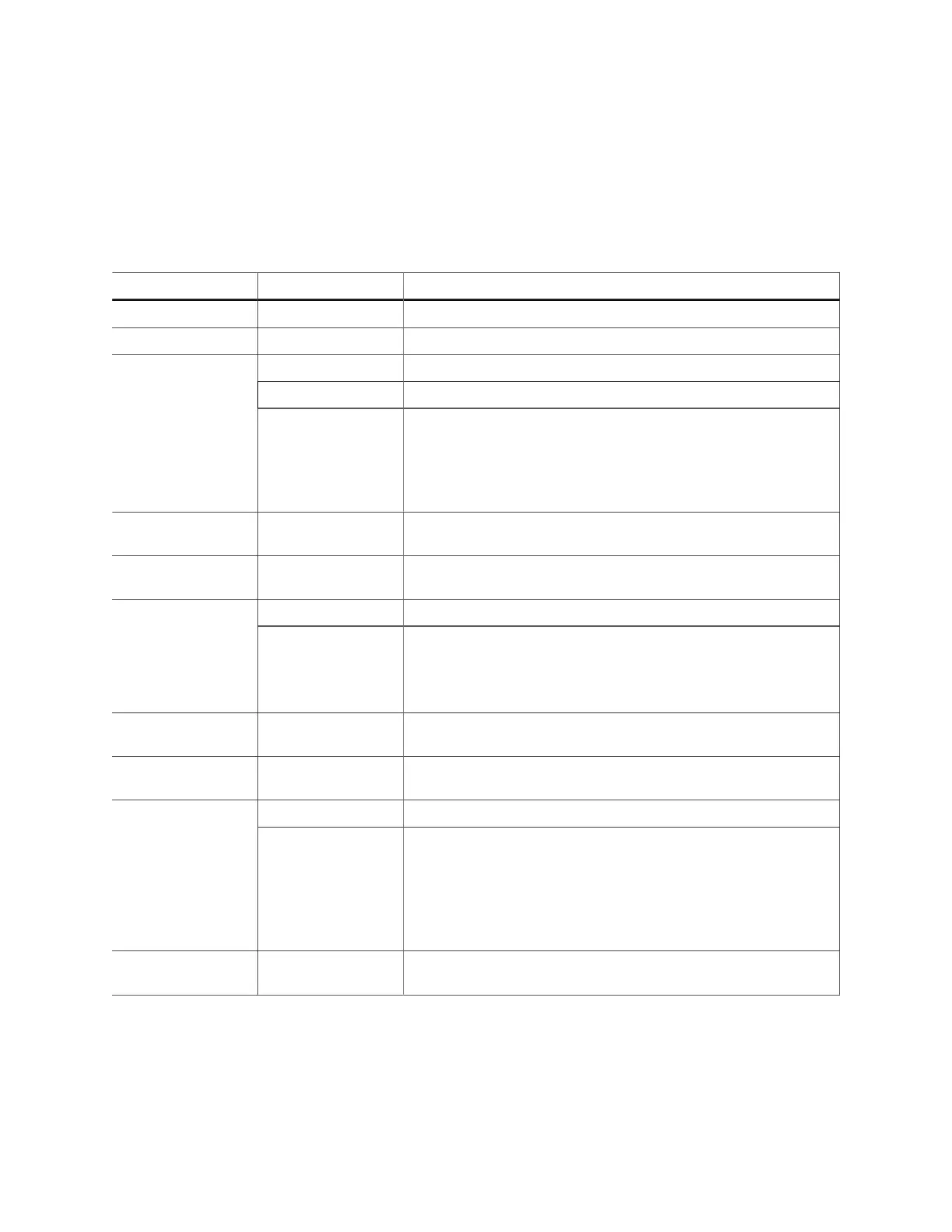

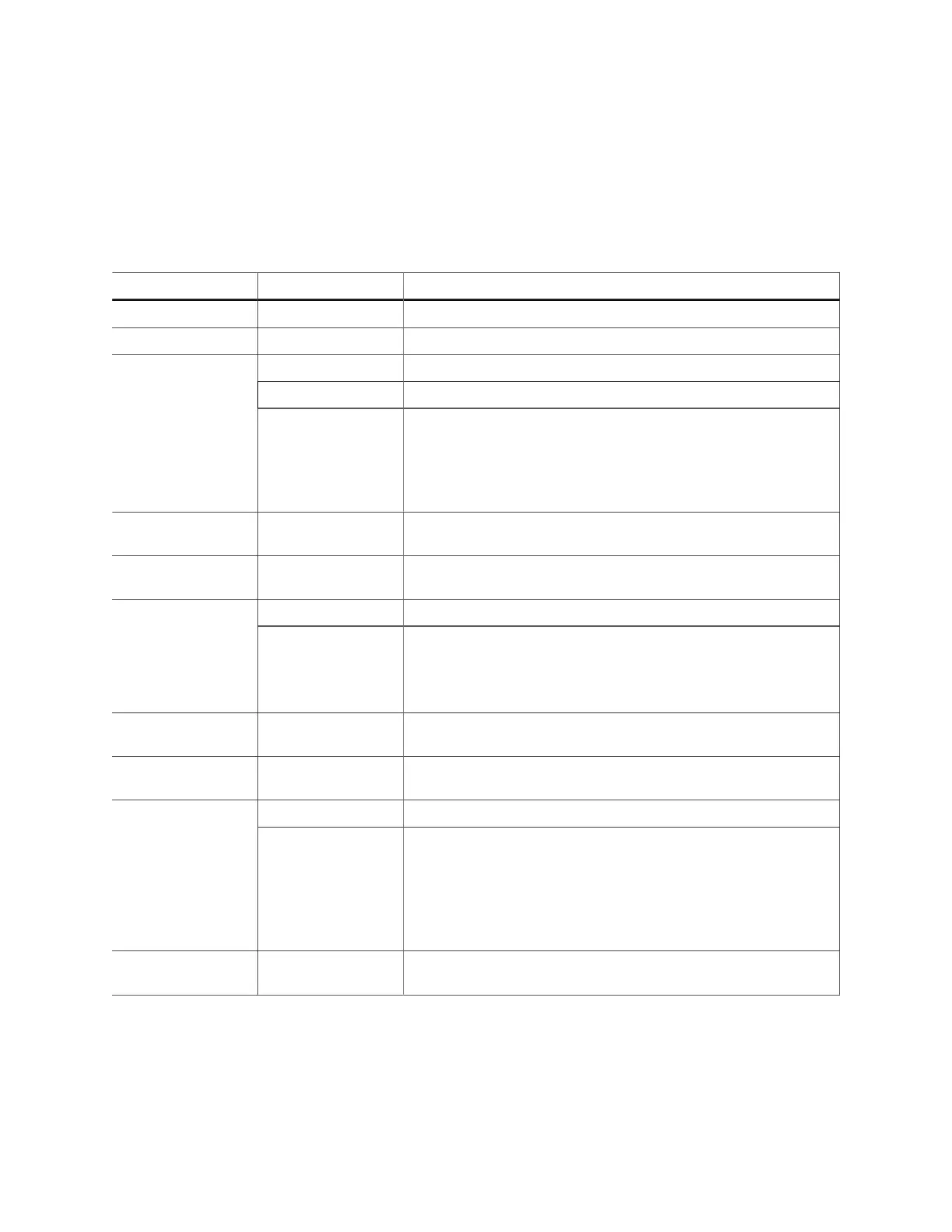

Table 42: LVDS TX Options

Option Choices Description

Instance Name User defined

LVDS Resource Resource list Choose a resource.

lvds, sublvds, custom Use for LVDS, RSDS, and mini-LVDS

sublvds

Output Differential

Type

custom Choose this option when you want to use a VREF pin to specify the

differential.

Set the GPIO input connection type to vref.

Choose a GPIO pin with that supports VREF in the same bank as

the LVDS TX resource.

Output Differential,

VOD

Typical, large, small The actual voltage depends on this setting and the diffential type

and is shown in the Block Summary Value field.

Output-Pre-

Emphasis

high, medium-high,

medium-low, low

serial data output Use the transmitter as a simple output buffer or serialized output.Mode

reference clock

output

Use the transmitter as a clock output.

Specify the serial and parallel clocks.

When choosing this mode, the serialization width should match

the serialization for the rest of the LVDS bus.

Output Pin/Bus

Name

User defined Output pin or bus that feeds the LVDS transmitter parallel data.

The width should match the serialization factor.

Output Enable Pin

Name

User defined Use with serial data output mode.

On Use as a simple buffer.Enable Serialization

Off Use as an LVDS serializer:

• Optionally enable half rate serialization.

• Choose a value of 2, 3, 4, 5, 6, 7, 8, or 10 (1 is a simple buffer). A

value of 9 is not legal.

• Specify the serial clock and parallel clock.

• Specify reset pin name.

Static Mode Delay

Setting

0 - 63 Choose the amount of static delay, each step adds approximately

25 ps of delay.

The maximum LVDS rate is 1.6 Gbps.

• Half rate calculation—serial clock frequency = parallel clock frequency * (serialization / 2)

• Full rate calculation—serial clock frequency = parallel clock * serialization

The serial clock must have a phase shift that is between 45 degrees and 135 degrees. Both

clocks must come from the same PLL.

www.efinixinc.com 73

Loading...

Loading...