Titanium Interfaces User Guide

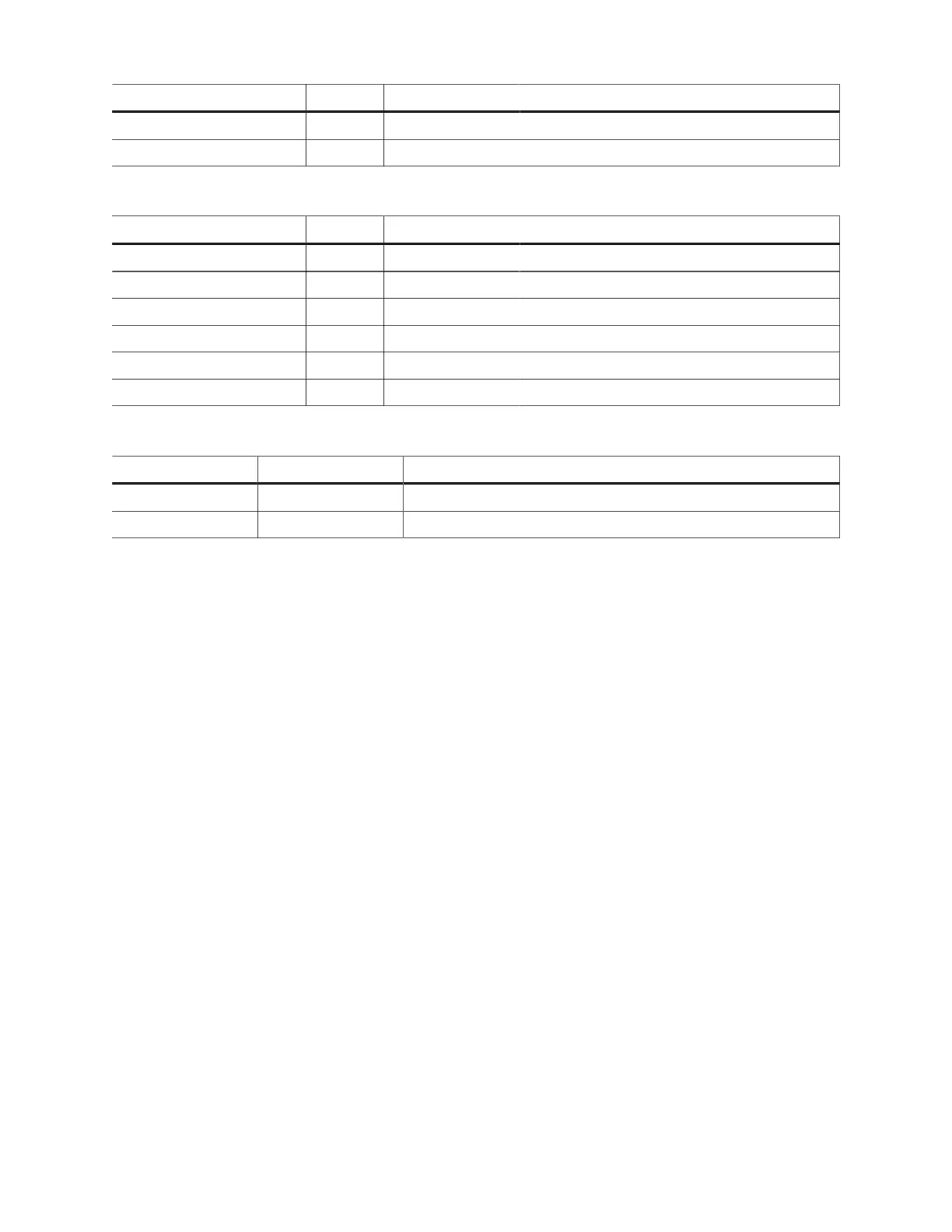

Signal Direction Clock Domain Notes

LDPT_TX_VALID Input ESC_CLK Lane 0 LPDT TX Data Valid.

LPDT_TX_READY Output ESC_CLK Lane 0 LDPT TX Data Ready.

Table 59: MIPI RX D-PHY ULP Sleep Mode Signals (Interface to FPGA Fabric)

Signal Direction Clock Domain Notes

ULPS_TX_ENTER Input ESC_CLK Lane 0 Enter ULPS Mode.

ULPS_TX_EXIT Input ESC_CLK Lane 0 Exit ULPS Mode.

ULPS_CLK_ENTER Output N/A CLK0 Enter ULPS Mode.

ULPS_CLK_ACTIVEN Output N/A CLK0 is in ULPS (Active Low).

ULPS_LANn_ENTER Output ESC_LANn_CLKOUT Lane n Enter ULPS Mode.

ULPS_LANn_ACTIVEN Output N/A Lane n is in ULPS (Active Low).

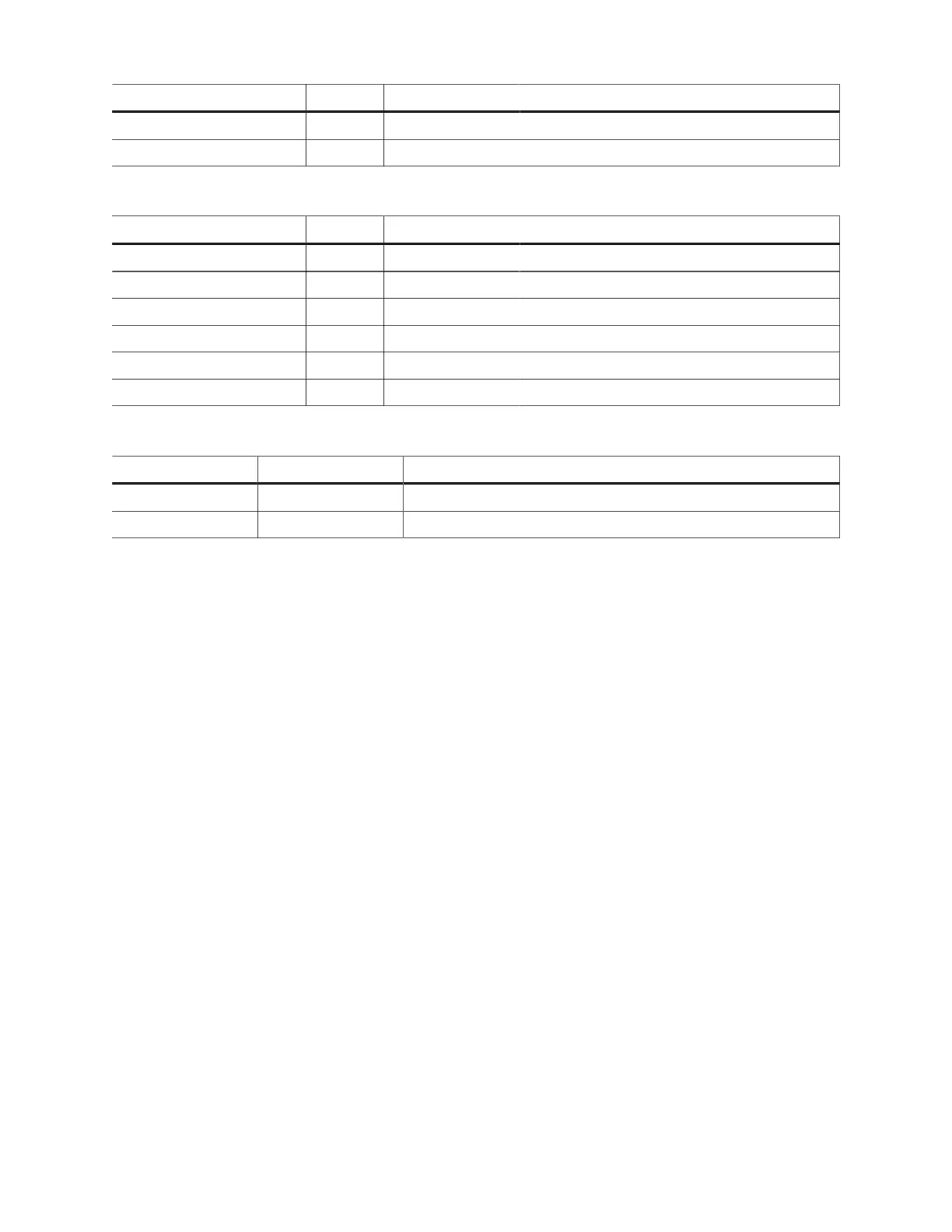

Table 60: MIPI RX D-PHY Pads

Pad Direction Description

RXDP[4:0] Bidirectional MIPI transceiver P pads.

RXDN[4:0] Bidirectional MIPI transceiver N pads.

MIPI TX D-PHY

The MIPI TX D-PHY is a transmitter interface designed to transmit data and the control

information of MIPI CSI, DSI, or other associated protocols. The MIPI TX D-PHY

comprises of one clock lane and up to four data lanes for a single-channel configuration. The

www.efinixinc.com 113

Loading...

Loading...