Titanium Interfaces User Guide

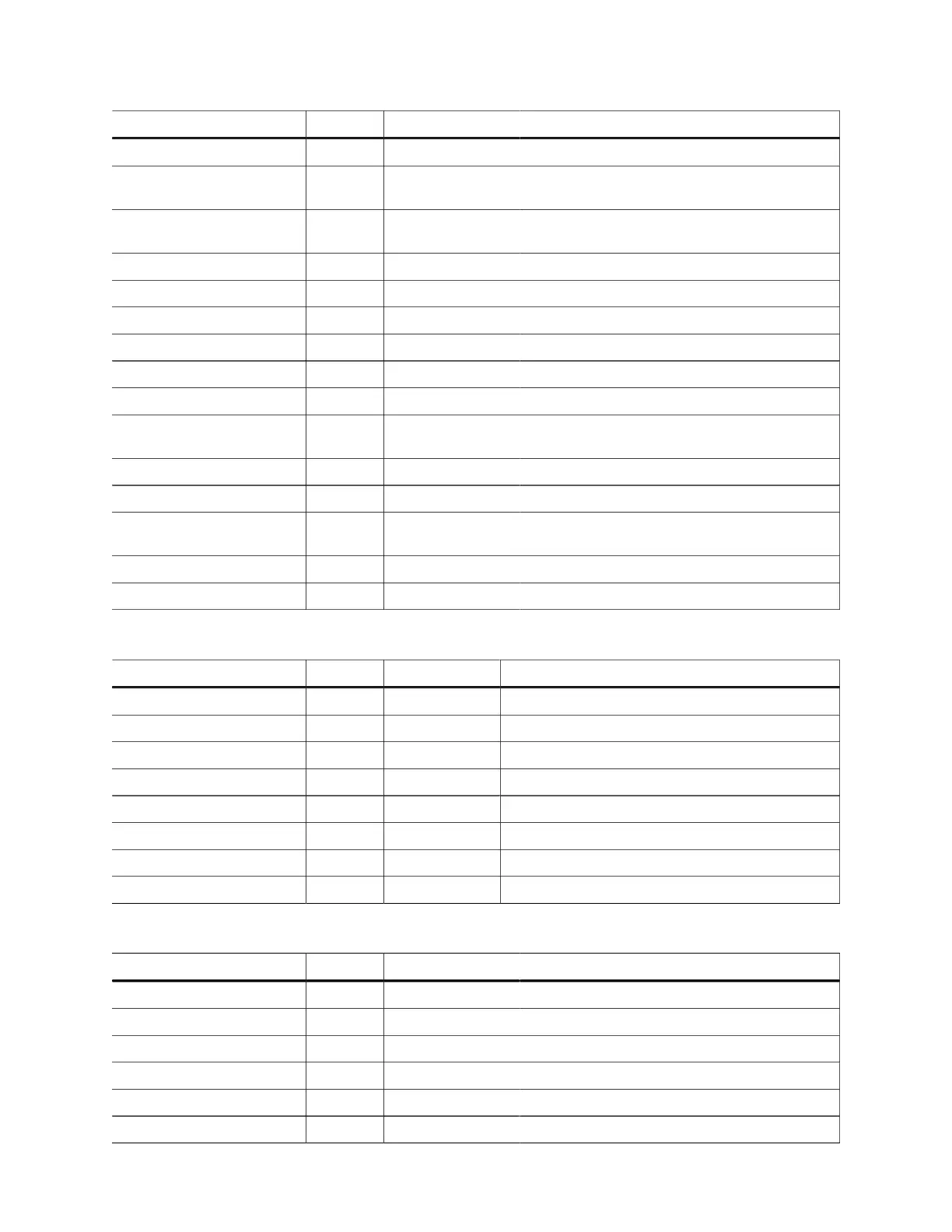

Table 56: MIPI RX D-PHY Control and Status Signals (Interface to FPGA Fabric)

Signal Direction Clock Domain Notes

RESET Input N/A Reset. Disables PHY and reset the digital logic.

RST0_N Input BYTE_CLKOUT Asynchronous FIFO reset and synchronous out

of reset.

RST1_N Input BYTE_CLKOUT Asynchronous FIFO reset and synchronous out

of reset.

STOPSTATE_CLK Output N/A Lane in Stop State.

STOPSTATE_LANn Output N/A Data Lane in Stop State (Lane N).

ESC_LANn_ERROR Output N/A Lane n Escape Command Error.

LINESTATE_LANn_ERROR Output N/A Lane n Has Line State Error.

REQUEST_TX_ESC Input ESC_CLK Lane 0 Request TX Escape Mode.

TURNAROUND_REQ Input ESC_CLK Lane 0 Request Turnaround.

FORCE_RX Input N/A Lane 0 Force Lane into Receive Mode/Wait for

Stop State.

SEND_TRIGGER [3:0] Input ESC_CLK Lane 0 Send a Trigger Event.

RECV_TRIGGER [3:0] Output ESC_LAN0_CLKOUT Lane 0 Received a Trigger Event.

DIRECTION Output N/A Lane 0 Transmit/Receive Direction (0 = TX, 1 =

RX).

CONTENTION_ERROR0 Output N/A Lane 0 Contention Error when driving 0.

CONTENTION_ERROR1 Output N/A Lane 0 Contention Error when driving 1.

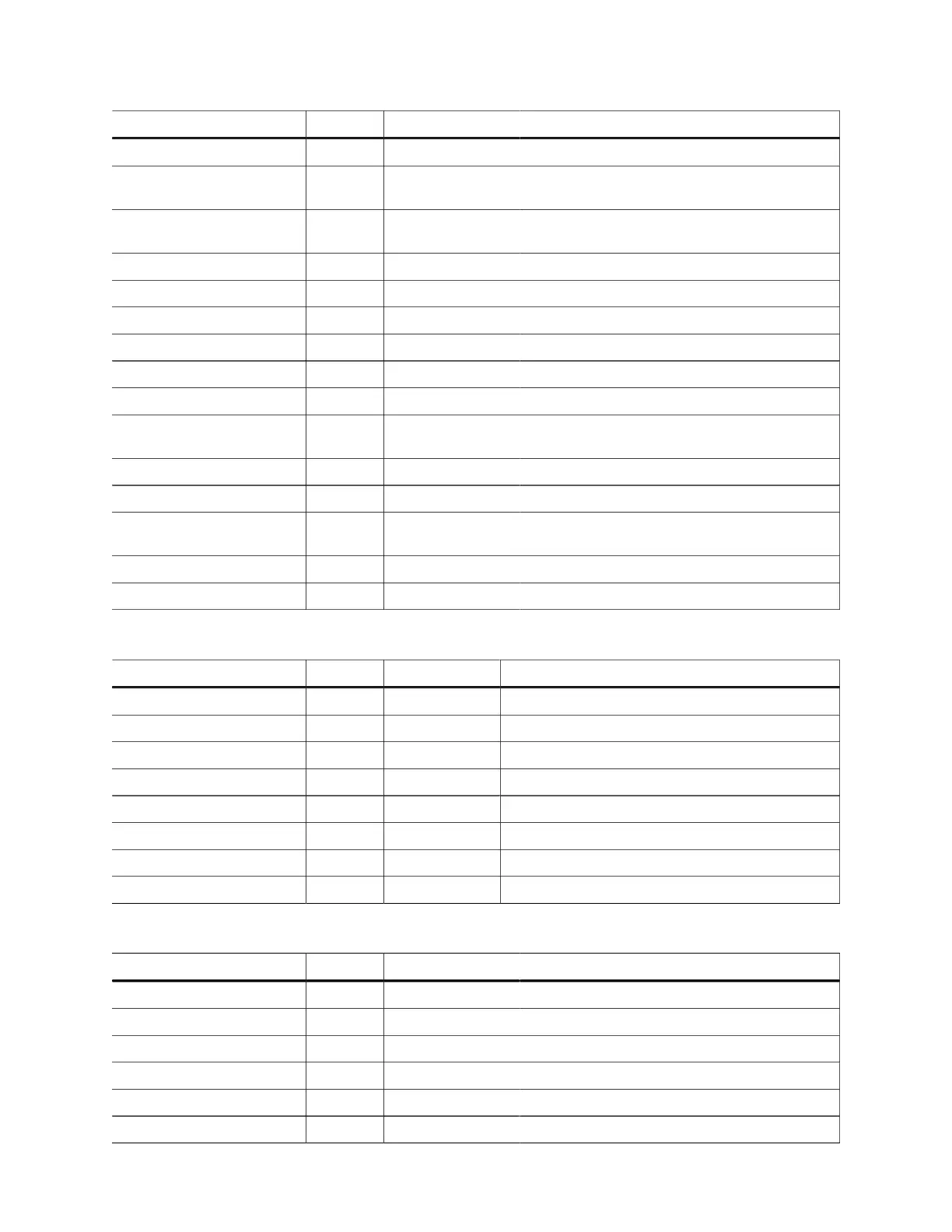

Table 57: MIPI RX D-PHY High Speed Mode Signals (Interface to FPGA Fabric)

Signal Direction Clock Domain Notes

HS_CLK_ACTIVE Output N/A HS Clock Lane Active.

HS_LANn_ACTIVE Output BYTE_CLKOUT HS Reception Active.

HS_LANn_VALID Output BYTE_CLKOUT HS Data Receive Valid .

HS_LANn_SYNC Output BYTE_CLKOUT HS Reveiver Sync. Observed.

HS_LANn_SKEWCAL Output BYTE_CLKOUT HS Reveiver DeSkew Burst Received.

HS_LANn_DATA [15:0] Output BYTE_CLKOUT HS Receive Data.

HS_LANn_SOT_ERR Output BYTE_CLKOUT State-of-Transmission (SOT) Error.

HS_LANn_SOTSYNC_ERROR Output BYTE_CLKOUT SOT Sync. Error.

Table 58: MIPI RX D-PHY Low-Power Data Receive Mode Signals (Interface to FPGA Fabric)

Signal Direction Clock Domain Notes

LPDT_RX_ENTER Output ESC_LAN0_CLKOUT Lane 0 enter LPDT RX Mode.

LPDT_RX_DATA [7:0] Output ESC_LAN0_CLKOUT Lane 0 LPDT RX Data.

LPDT_RX_VALID Output ESC_LAN0_CLKOUT Lane 0 LPDT RX Data Valid.

LPDT_RX_SYNC_ERR Output N/A Lane 0 LPDT RX Data Sync. Error.

LPDT_TX_ENTER Input ESC_CLK Lane 0 Enter LPDT TX Mode.

LPDT_TX_DATA [7:0] Input ESC_CLK Lane 0 LPDT TX Data.

www.efinixinc.com 112

Loading...

Loading...