Titanium Interfaces User Guide

Chapter 3

Clock and Control Networks

Contents:

• Clock Sources that Drive the Global and Regional Networks

• Configuring the Dynamic Clock Multiplexers

• Driving both the Global and Regional Networks

• Design Check: Clock Control Messages

The clock and control network is distributed through the FPGA to provide clocking for the

core's LEs, memory, DSP blocks, I/O blocks, and control signals. The FPGA has global

signals that can be used as either clocks or control signals. The global signals are balanced

trees that feed the whole FPGA.

The FPGA also has regional signals that can only reach certain FPGA regions, including the

top or bottom edges. The FPGA has regional networks for the core, right interface, and left

interface blocks. The top and bottom interface blocks have 1 regional clock network each.

You can drive the right and left sides of each region independently. Each region also has a

local network of clock signals that can only be used in that region.

The core's global buffer (GBUF) blocks drive the global and regional signals. Signals from the

core and interface can drive the GBUF blocks.

Each network has dedicated enable logic to save power by disabling the clock tree. The logic

dynamically enables/disables the network and guarantees no glitches at the output.

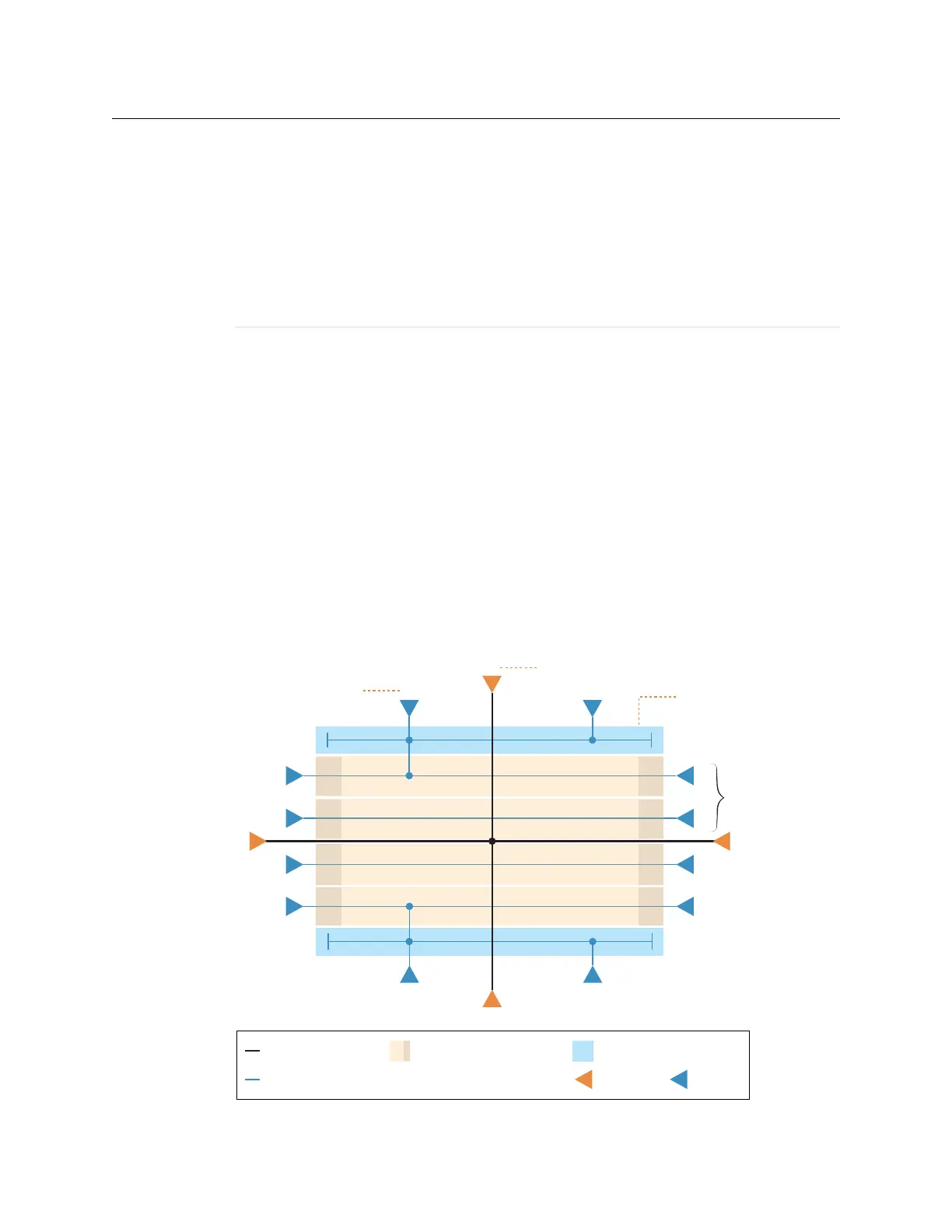

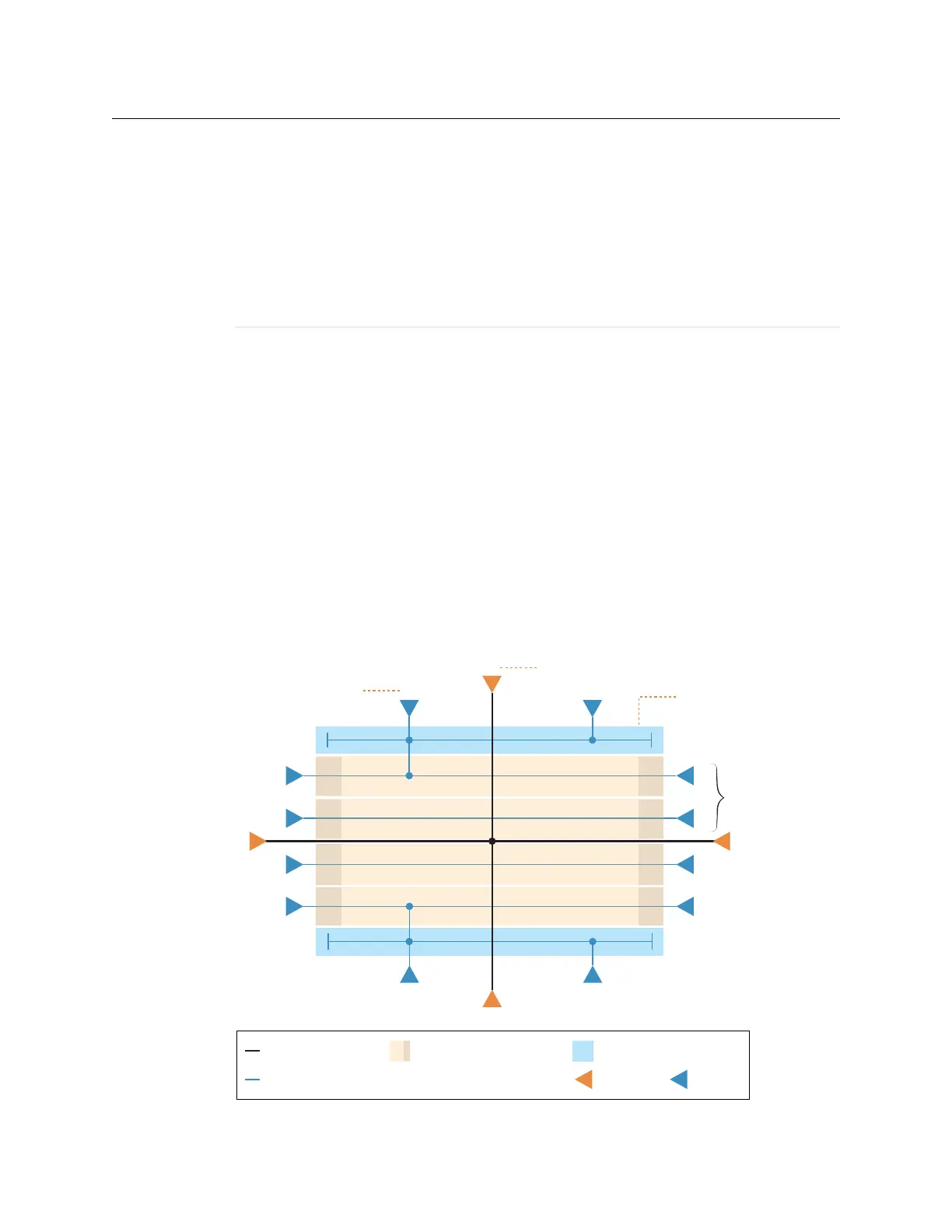

Figure 9: Global and Regional Clock Network Overview (Ti35, Ti60)

8

8

RBUF

Interface Only Region

Regions for

Core and Interface

Interface Only

Region

www.efinixinc.com 24

Loading...

Loading...