Titanium Interfaces User Guide

MIPI Lane Pads

Table 52: MIPI Lane Pads

Signal Direction Description

P Output Differential pad P.

N Output Differential pad N.

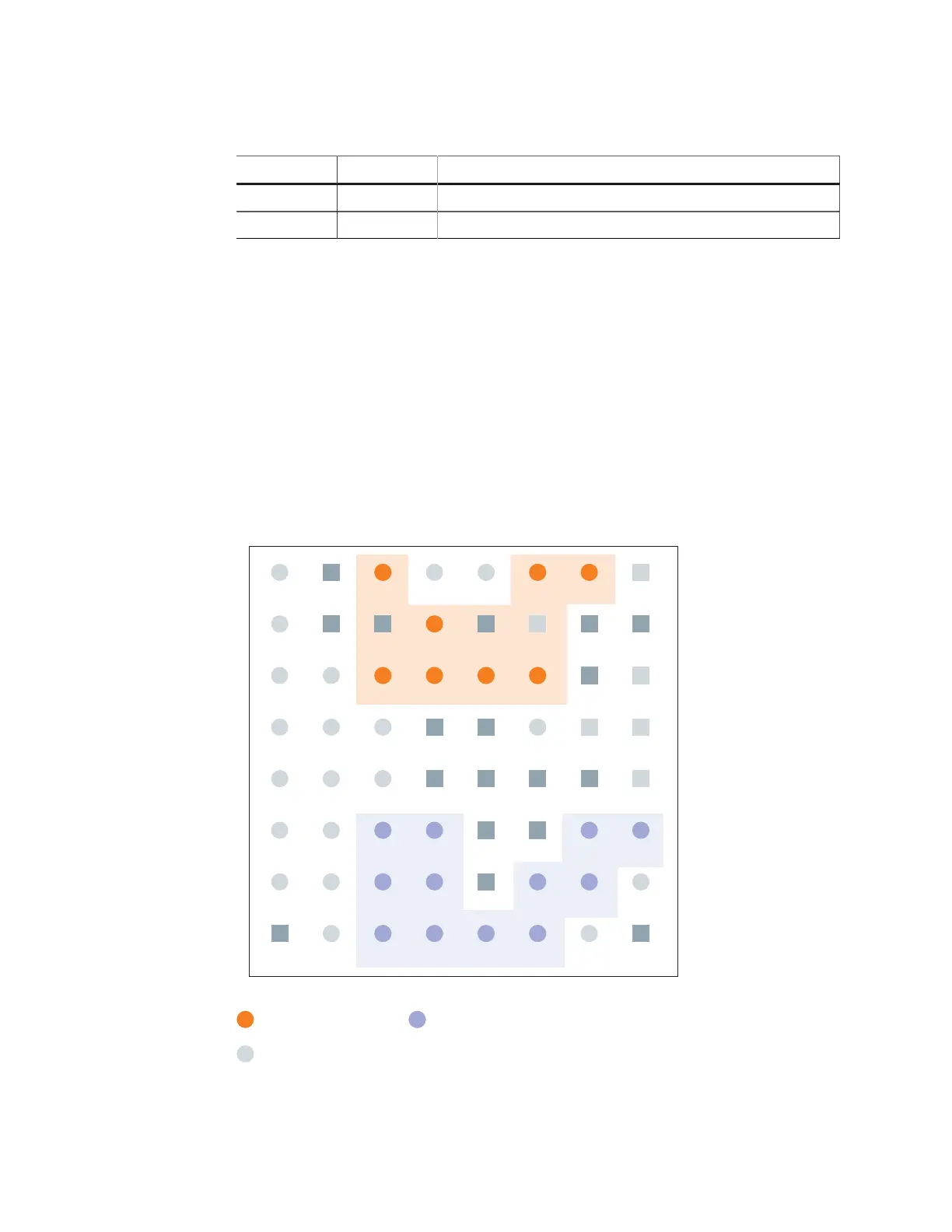

MIPI Groups by Package

You can use multiple HSIO as MIPI D-PHY lanes to build complete MIPI interfaces with

one clock lane and up to 8 data lanes.

• For MIPI TX interfaces, you can use any lane anywhere on the FPGA.

• For MIPI RX interfaces, the number of data lanes is restricted by the number of lanes in

the MIPI group. These groups vary depending on the package.

The following figures show the MIPI RX groups for each package. The Resource Assigner

also shows the group in the Block Summary's Feature field.

Figure 38: 64-Ball WLCSP MIPI RX Groups

C D E F G H

MIPI RX group I6

TMS

TCK

TDI

GPIOR_P_00

PLLIN0

REF_RES_4A

GND

GPIOL_N_17

GPIOL_N_15

TEST_N

GPIOL_N_01

CCK

GPIOL_P_01

SSL_N

REF_RES_1A

VCCIO1A_4B

TDO

GPIOL_P_13

CBSEL0

GPIOR_P_09

CLK10_P

GND

GPIOR_P_02

CDI24

GPIOR_P_03

CDI26

VCCAUX GND

VCCIO2B_3A

_3B_4A

VCC

VCCA_BR

GPIOR_N_01

CDI23

GPIOR_N_00

CDI22

GPIOR_P_01

EXTFB

GPIOR_P_05

CDI30

GPIOR_N_05

CDI31

GPIOR_P_04

CDI28

GPIOR_N_04

CDI29

REF_RES_3B

VCC

GND

www.efinixinc.com 99

Loading...

Loading...